VHDL(一)模拟部分 电子线路仿真实验报告 实验名称: 软件和实验箱介绍 姓 名: 申红霞 学 号: 080404108 班 级: 08通信一班 时 间: 10

02 南京理工大学紫金学院电光系 一、 实验目的 1

讲解QuartusⅡ软件和实验箱的使用

利用原理图输入法实现4 位串行进位加法器

重点掌握软件使用过程中工程建立、原理图输入方法、编译、仿真、管脚配置等

二、 实验原理 1

加法器原理 全加器真值表如图1 所示: 加法器真值表 全加器表达式为: Si=Ai⊕ Bi⊕ Ci-1 Ci=( Ai⊕ Bi) Ci-1+AiBi 全加器逻辑符号如图2 所示: 全加器逻辑符号 2

利用全加器可以构成4 位串行进位加法器,逻辑符号如图3 所示: 4 位串行进位加法器逻辑符号图 三、 实验内容 1

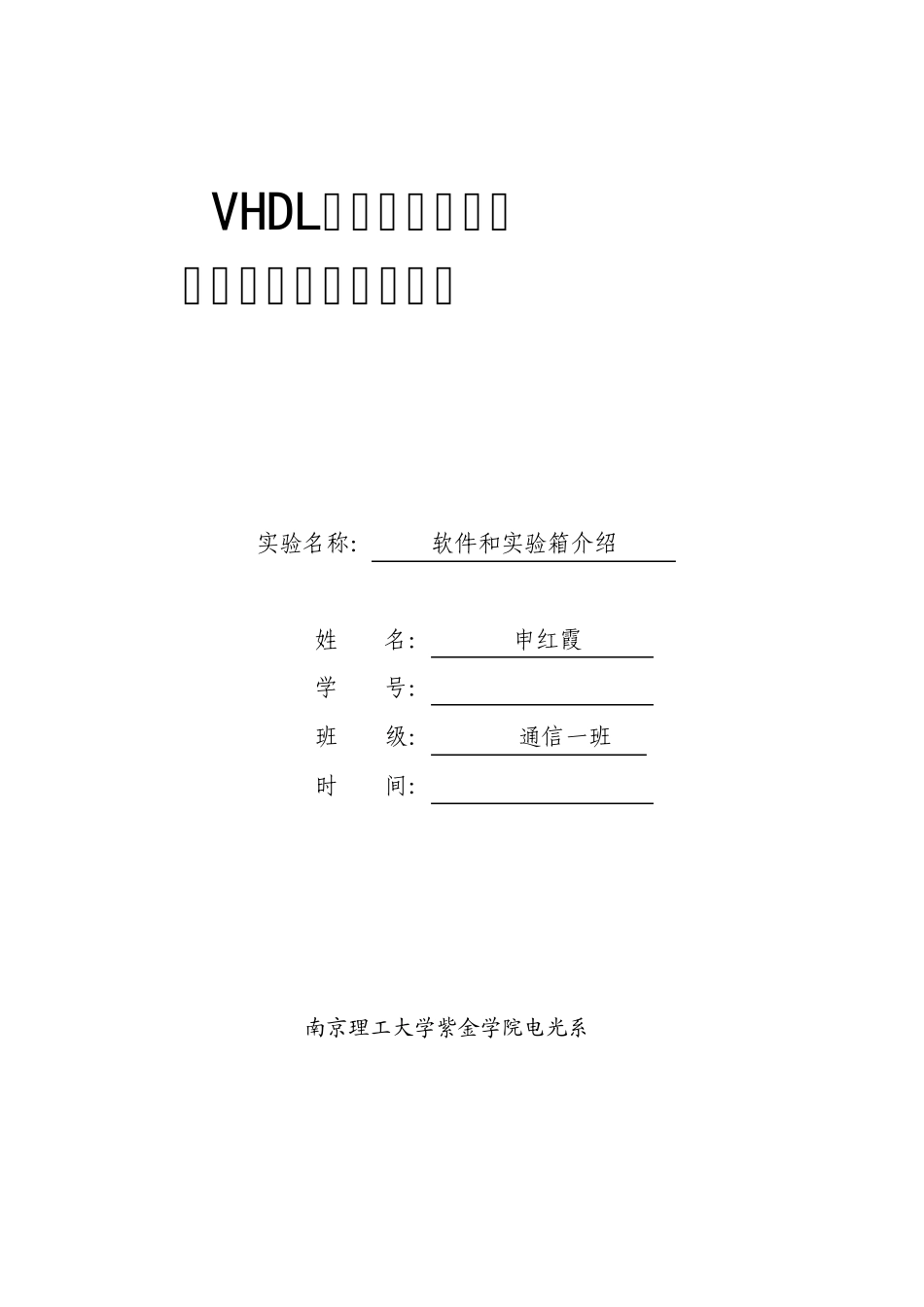

新建文件夹,在所新建的文件夹中利用QuartusⅡ软件建立新工程,设计原理图输入的一 位全加器电路,如图4 所示: 图 4、 一位全加器电路 2

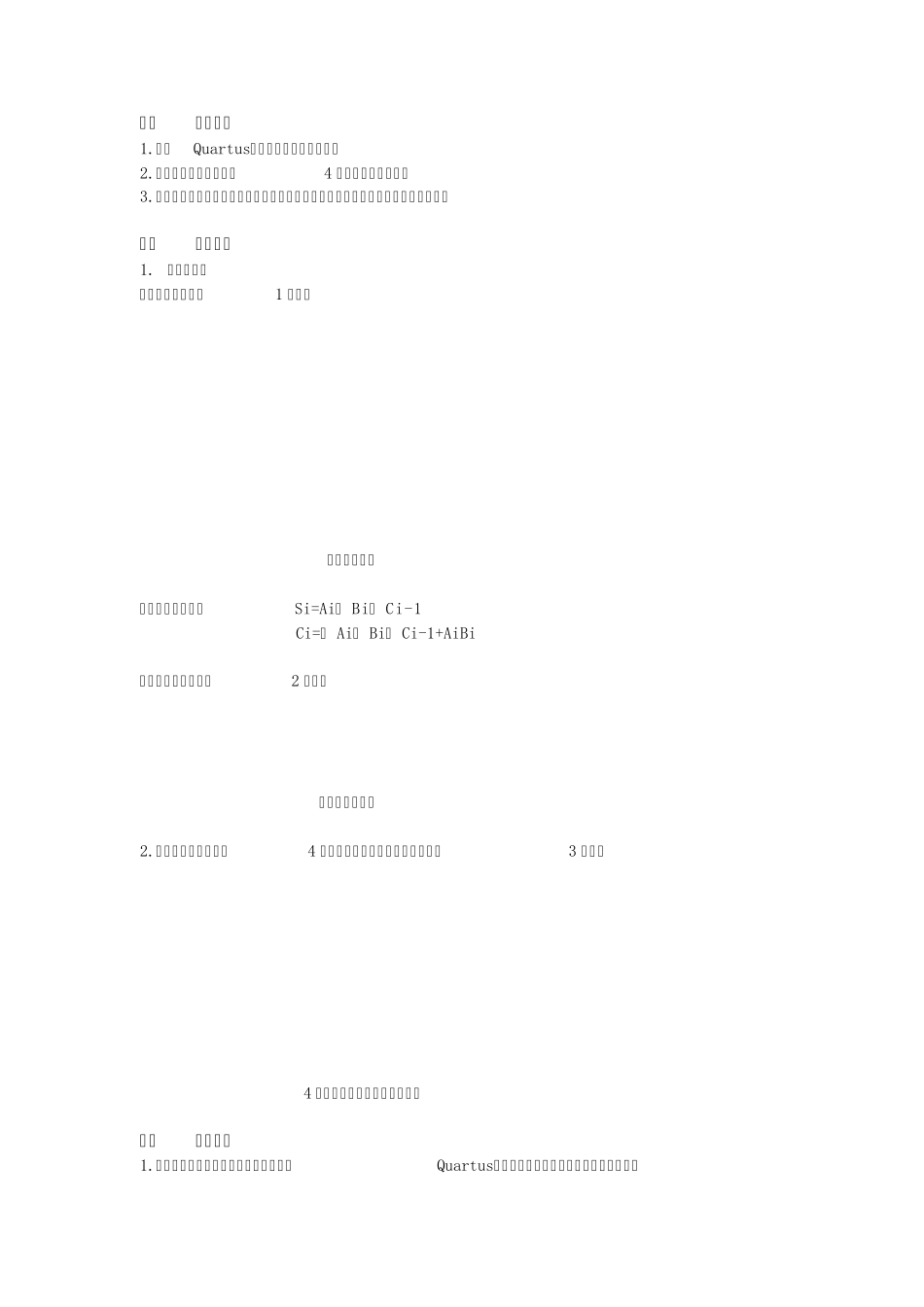

对该图进行全编译,编译成功后,建立矢量波形文件,验证所设计的一位全加器电路的正确性,时序仿真结果和功能仿真结果如下图所示: 图 5、 时序仿真结果 图 6、 功能仿真结果 由仿真波形分析可知,该全加器设计正确

将设计好的全加器生成一个模块,如图7 所示: 图 7、一位全加器器件 4

将 4 个全加器串联,再添加相应的管脚和原件构成四位串行进位加法器,如图8 所示: 图 8、 四位串行进位加法器电路图 5.将此文件设置为顶层文件,对该图进行全编译,编译成功后,建立矢量波形文件,添加相应的节点,为输入信号赋初值,功能仿真结果和时序仿真结果如下图: 图 9、 功能仿真结果 图 10、 时序仿真结果 由仿真波形可知,电路设计正确

6.利用模式实验箱来验证设计电路的正确性,设置管脚,管脚配置图如图11 所示: 图 1