By Poordusk (poordusk@hotmail

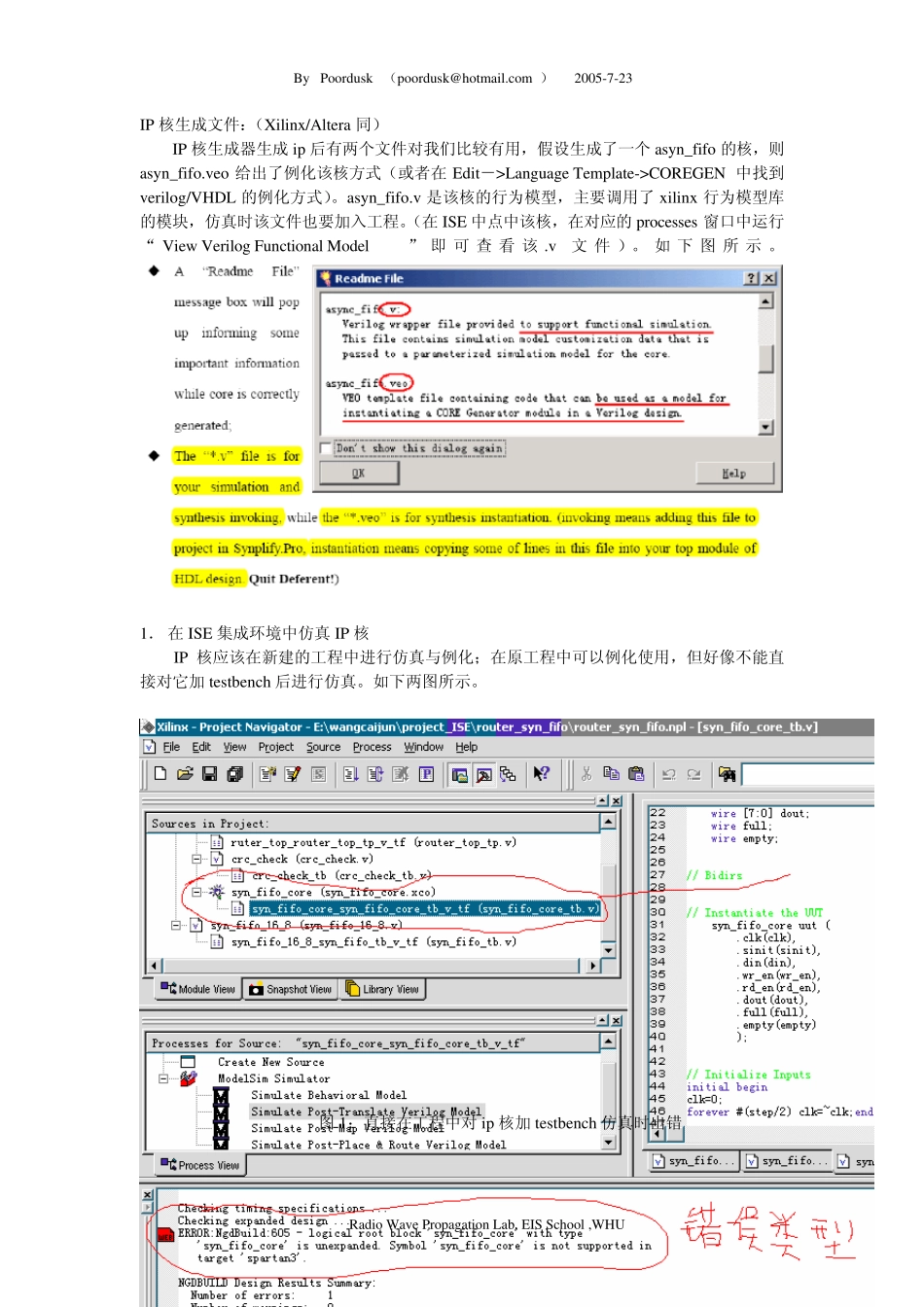

com ) 2005-7-23 IP 核生成文件:(Xilinx/Altera 同) IP 核生成器生成ip 后有两个文件对我们比较有用,假设生成了一个asyn_fifo 的核,则asyn_fifo

veo 给出了例化该核方式(或者在Edit->Language Template->COREGEN 中找到verilog/VHDL 的例化方式)

asyn_fifo

v 是该核的行为模型,主要调用了xilinx行为模型库的模块,仿真时该文件也要加入工程

(在ISE 中点中该核,在对应的processes 窗口中运行“ View Verilog Functional Model” 即 可 查 看 该

如 下 图 所 示

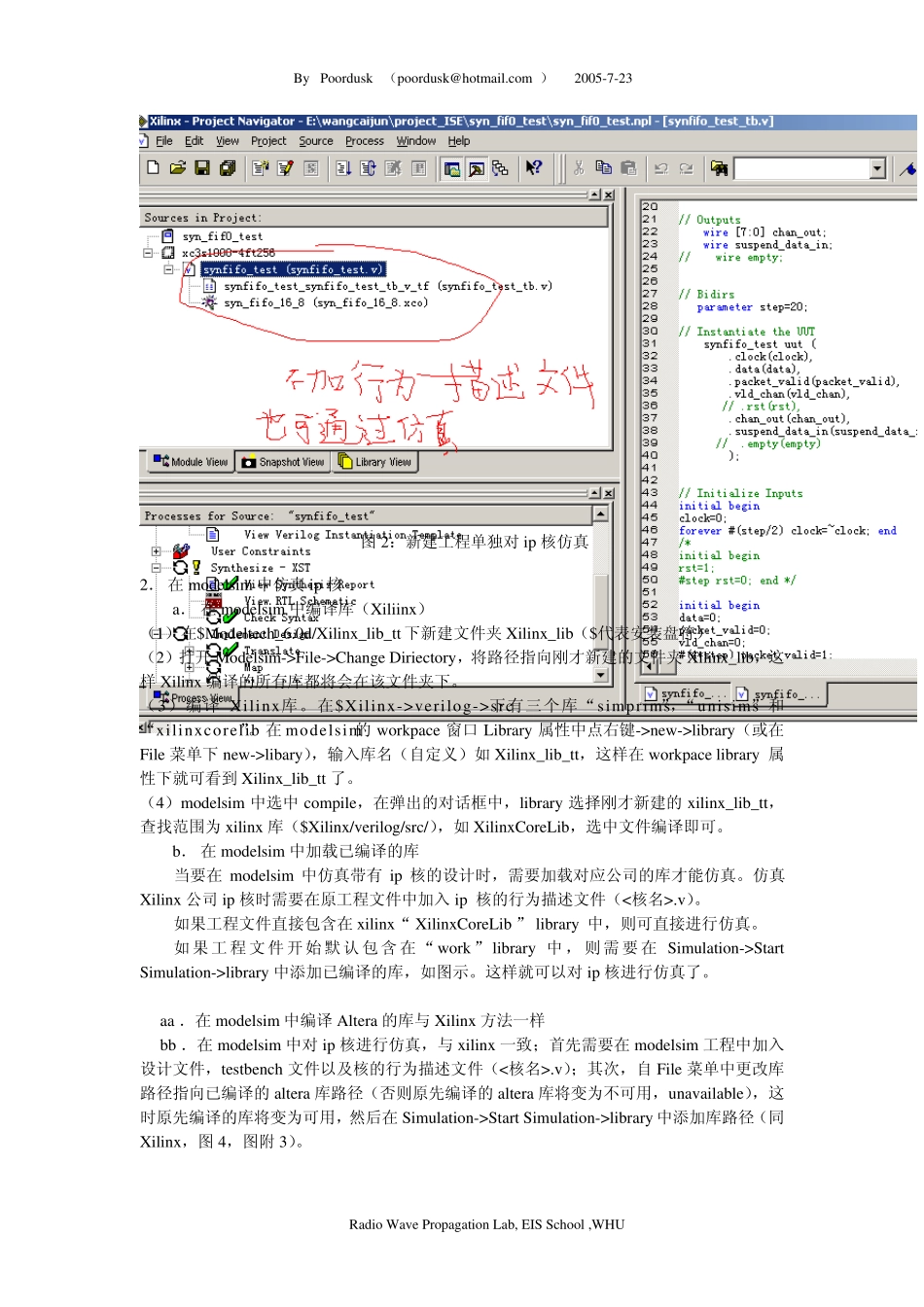

1. 在ISE 集成环境中仿真IP 核 IP 核应该在新建的工程中进行仿真与例化;在原工程中可以例化使用,但好像不能直接对它加testbench 后进行仿真

如下两图所示

图 1:直接在工程中对ip 核加testbench 仿真时出错 Radio Wave Propagation Lab, EIS School ,WHU By Poordusk (poordusk@hotmail

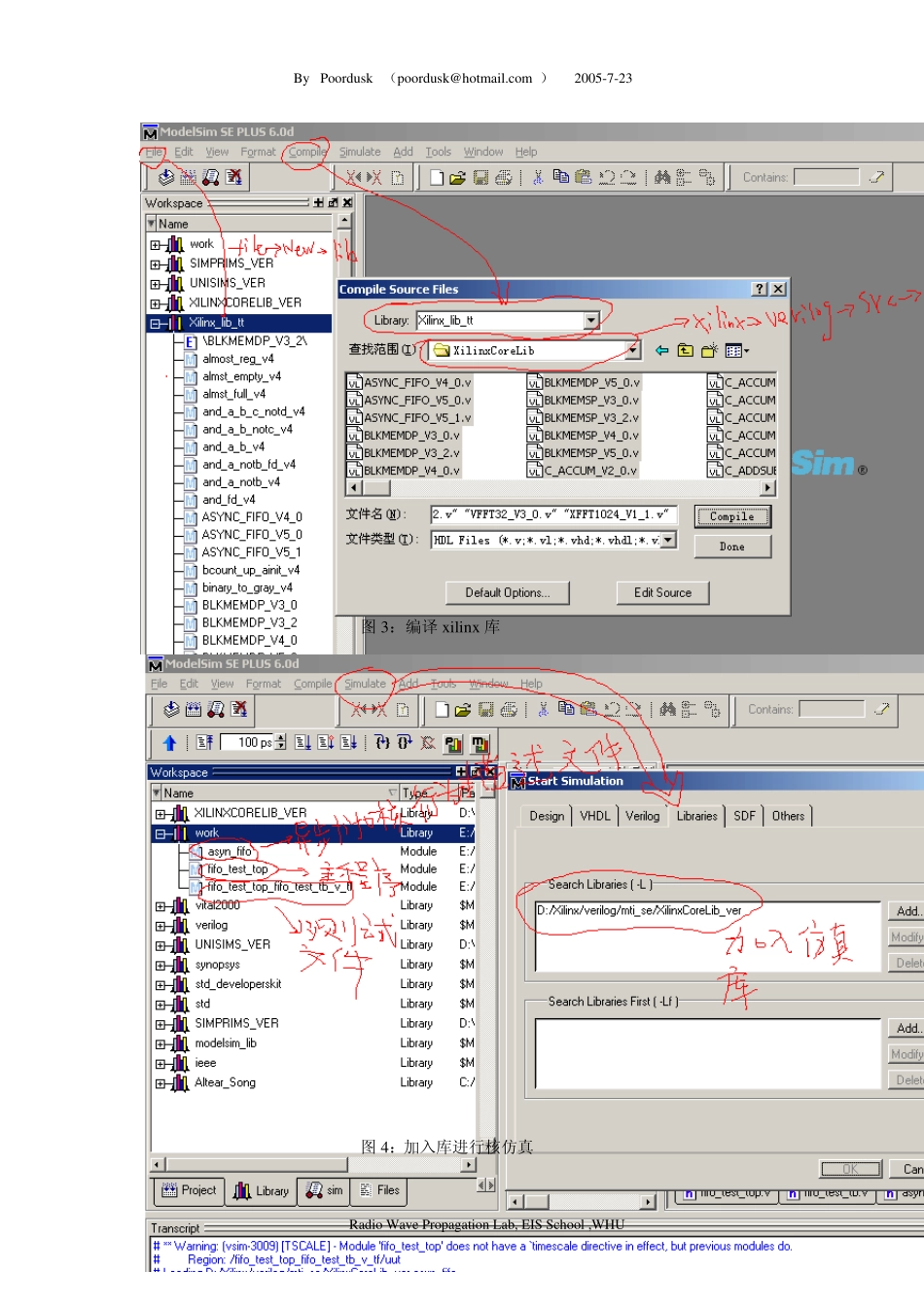

com ) 2005-7-23 图2:新建工程单独对ip 核仿真 2. 在modelsim 中仿真ip 核 a. 在modelsim 中编译库(Xiliinx) (1)在$Modeltech_6

0d/Xilinx_lib_tt 下新建文件夹Xilinx_lib($代表安装盘符) (2)打开Modelsim->File->Change Diriectory,将路径指向刚才新建的文件夹Xilinx_lib,这样Xilinx编译的所有库都将会在该文件夹下

(3)编译Xilinx库

在$Xilinx->verilog