实验四-序列检测 一、实验目的: 1

实验目的:通过学习硬件编程语言,掌握一般时序逻辑分析的方法

学会使用Verilog 语言编写实现任意序列检测

学会使用Verilog 编写测试文件testbech 的方法并在Modelsim 中实现时序仿真

二、实验设备 1

PC 机一台 2

Modelsim 软件 三、实验内容: 序列检测器是能够与从二进制码流中检测出一组特定序列的信号的时序电路

通过接受的序列号与检测其预设值比较,当检测到输入信号匹配时,输出响应的指示

设计序列检测器,要求能够识别序列“10010”

din 为数字码流的输入,z 是检测标记的输出,高电平表示“发现指定序列”,低电平表示“没有发现指定的序列”

检测序列“10010”时序输入与输出示例如下: T 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 … x 0 0 0 1 1 0 0 1 0 0 1 0 0 0 0 1 0 0 1 0 … z 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 1 … Table 1 - 序列检测时序输入与输出示例 1

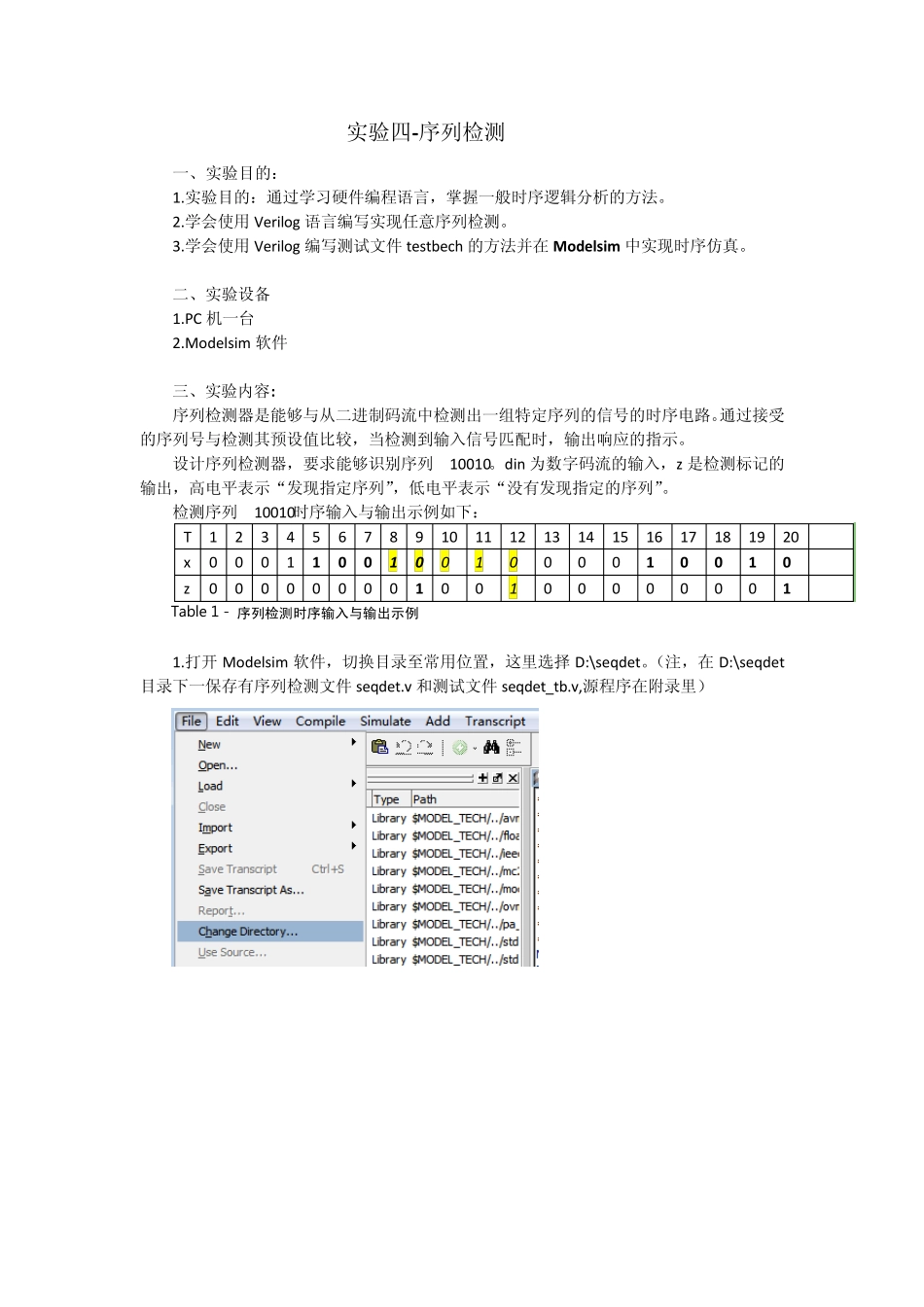

打开 Modelsim 软件,切换目录至常用位置,这里选择 D:\seqdet

(注,在D:\seqdet目录下一保存有序列检测文件seqdet

v 和测试文件seqdet_tb

v,源程序在附录里) 2

然后新建工程,File ->New ->Project,建立工程工程为seqdet,设置如下,并在接下来的步骤中添加序列检测文件seqdet

v 和测试文件seqdet_tb

编译文件 编译无误后,进行仿真 5

文件仿真 在弹出的窗口中选择Design->w ork->seqdet_tb,默认选中优化选项

选择OK 6

添加信号到wave 视图中