异步FIFO 设计文档 一、概述 在大规模 ASIC 或 FPGA 设计中,多时钟系统往往是不可避免的,这样就产生了不同时钟域数据传输的问题,其中一个比较好的解决方案就是使用异步FIFO 来作不同时钟域数据传输的缓冲区,这们既可以使相异时钟域数据传输的时序要求变得宽松,也提高了它们之间的传输效率

此文内容就是阐述异步FIFO的设计

二、设计原理 2

1 结构框图 Fig

1 如上图所示的同步模块 synchronize to write clk,其作用是把读时钟域的读指针 rd_ptr 采集到写时钟(wr_clk)域,然后和写指针 wr_ptr 进行比较从而产生或撤消写满标志位 wr_full;类似地,同步模块 synchronize to read clk 的作用是把写时钟域的写指针 wr_ptr 采集到读时钟域,然后和读指针 rd_ptr 进行比较从而产生或撤消读空标志位 rd_empty

另外还有写指针 wr_ptr 和写满标志位 wr_full 产生模块,读指针 rd_ptr 和读空标志位 rd_empty产生模块,以及双端口存储 RAM 模块

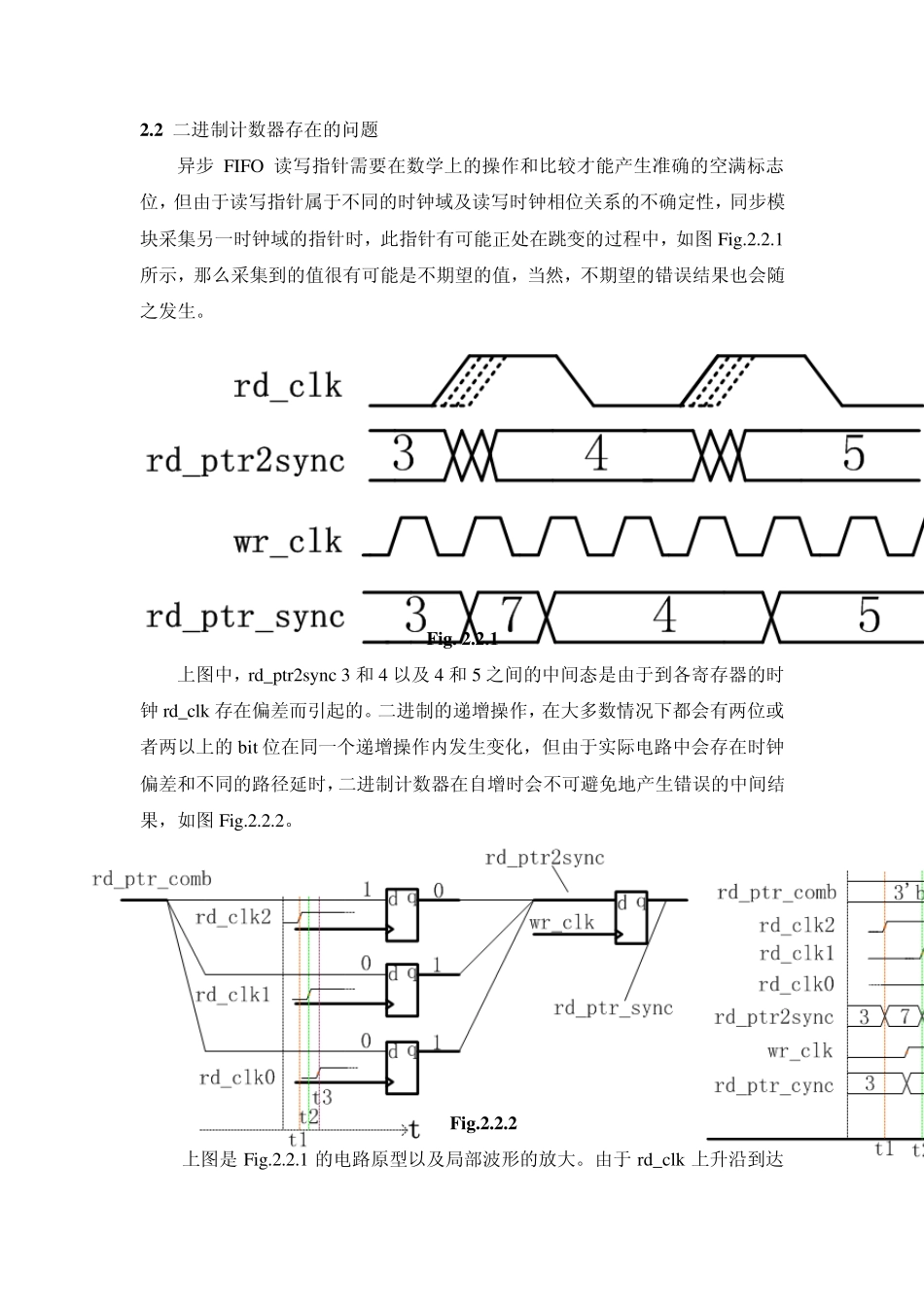

2 二进制计数器存在的问题 异步FIFO 读写指针需要在数学上的操作和比较才能产生准确的空满标志位,但由于读写指针属于不同的时钟域及读写时钟相位关系的不确定性,同步模块采集另一时钟域的指针时,此指针有可能正处在跳变的过程中,如图Fig

1所示,那么采集到的值很有可能是不期望的值,当然,不期望的错误结果也会随之发生

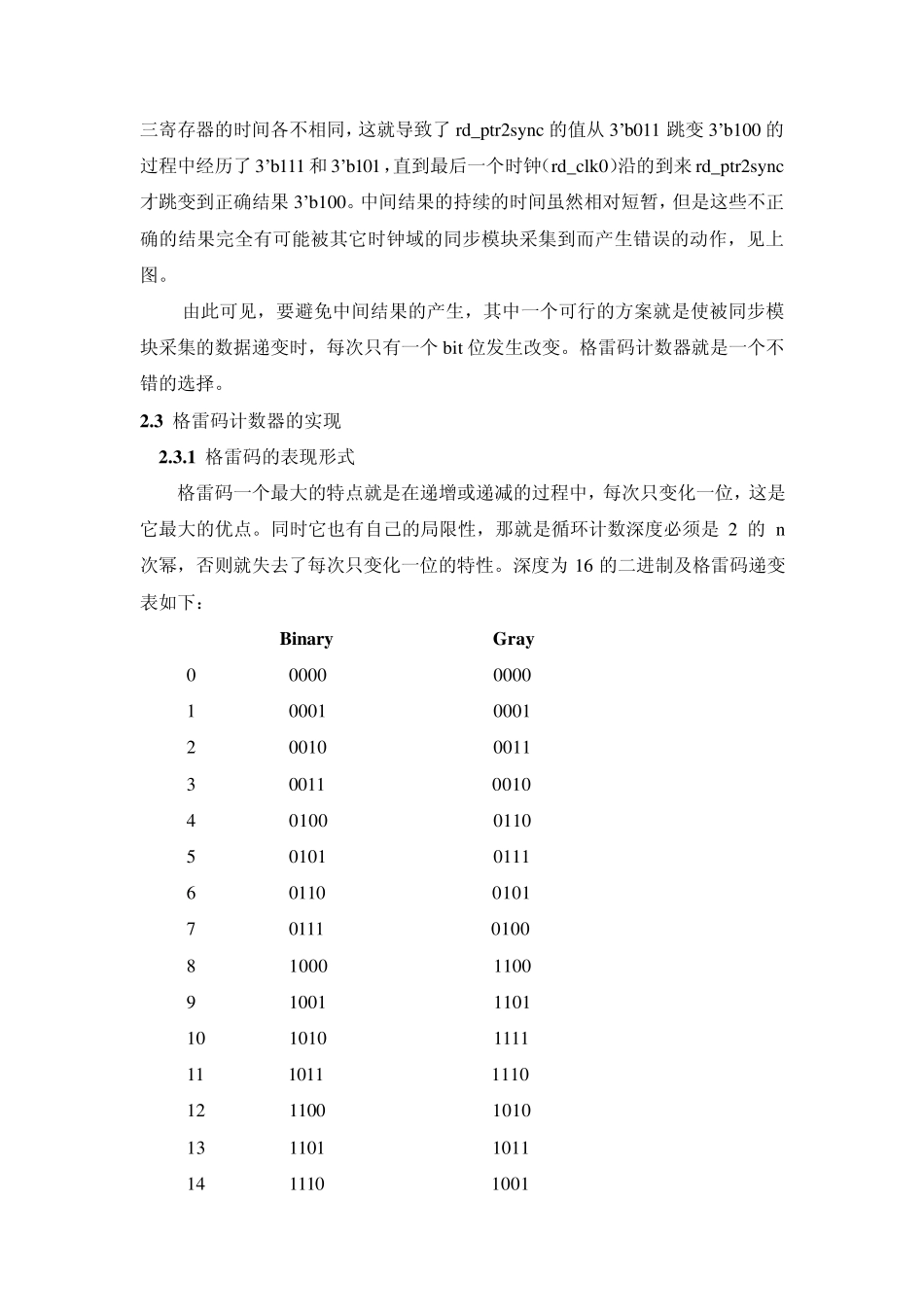

1 上图中,rd_ptr2sy nc 3 和4 以及4 和5 之间的中间态是由于到各寄存器的时钟rd_clk 存在偏差而引起的

二进制的递增操作,在大多数情况下都会有两位或者两以上的bit 位在同一个递增操作内发生变化,但由于实际电路中会存在时钟偏差和不同的路径延时,