一、实验目的 (1)熟练掌握分频器、各种进制的同步计数器的设计

(2)熟练掌握同步计数器的级联方法

(3)掌握数码管的动态显示驱动方式

(4)掌握计数器的功能和应用

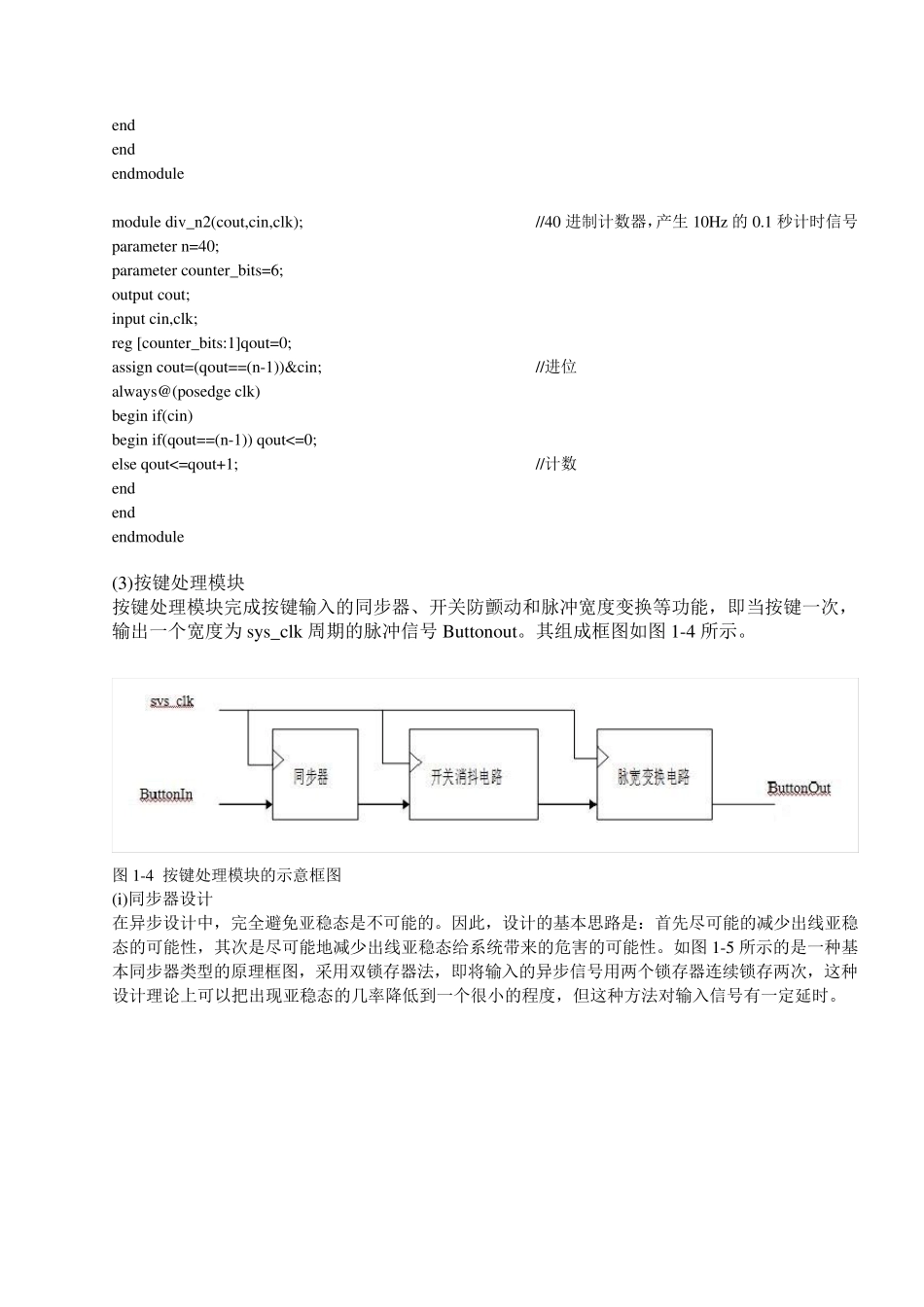

(5)理解开关防颤动的必要性

(6)掌握简单控制器的设计方法

二、实验内容和原理 1、实验设计要求: (1)计时范围0’0’

0’’~59’59’

9’’,分辨率为0

1s,用数码管显示计时值

(2)秒表有一个按键开关:当电路处于“初始”状态时,第一次按键,计时开始(“计时”状态);再次按键

计时停止(“停止”状态);第三次按键,计时器复位为0’0’

0’’,且电路恢复到“初始”状态

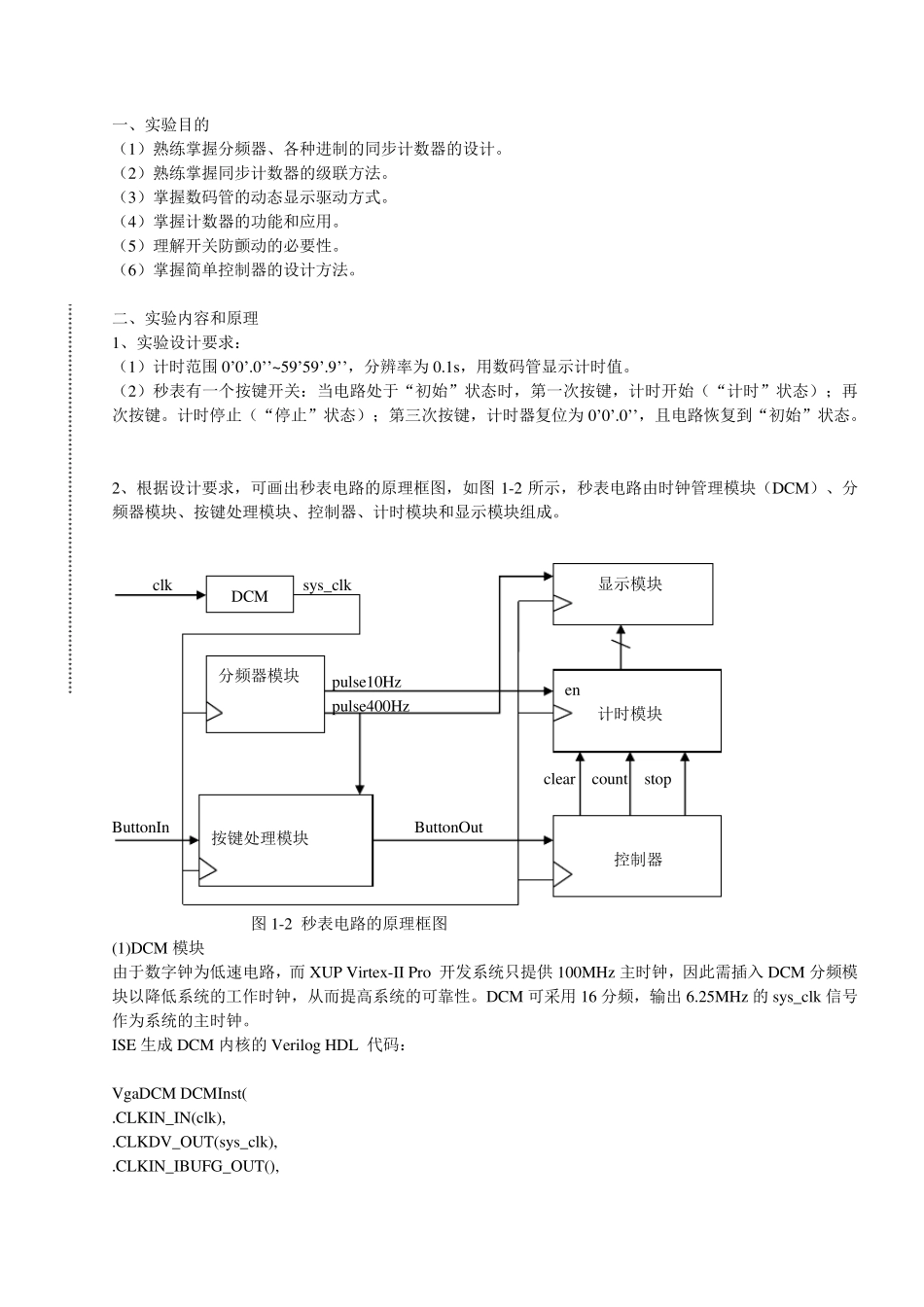

2、根据设计要求,可画出秒表电路的原理框图,如图 1-2 所示,秒表电路由时钟管理模块(DCM)、分频器模块、按键处理模块、控制器、计时模块和显示模块组成

clk sys_clk pulse10Hz pulse400Hz clear count stop ButtonIn ButtonOut 图 1-2 秒表电路的原理框图 (1)DCM 模块 由于数字钟为低速电路,而 XUP Virtex-II Pro 开发系统只提供 100MHz 主时钟,因此需插入 DCM 分频模块以降低系统的工作时钟,从而提高系统的可靠性

DCM 可采用16 分频,输出 6

25MHz 的sys_clk 信号作为系统的主时钟

ISE 生成 DCM 内核的Verilog HDL 代码: VgaDCM DCMInst(

CLKIN_IN(clk),

CLKDV_OUT(sys_clk),

CLKIN_IBUFG_OUT(), DCM 按键处理模块 分频器模块 en 计时模块 控制器 显示模块

CLK0_OUT(),

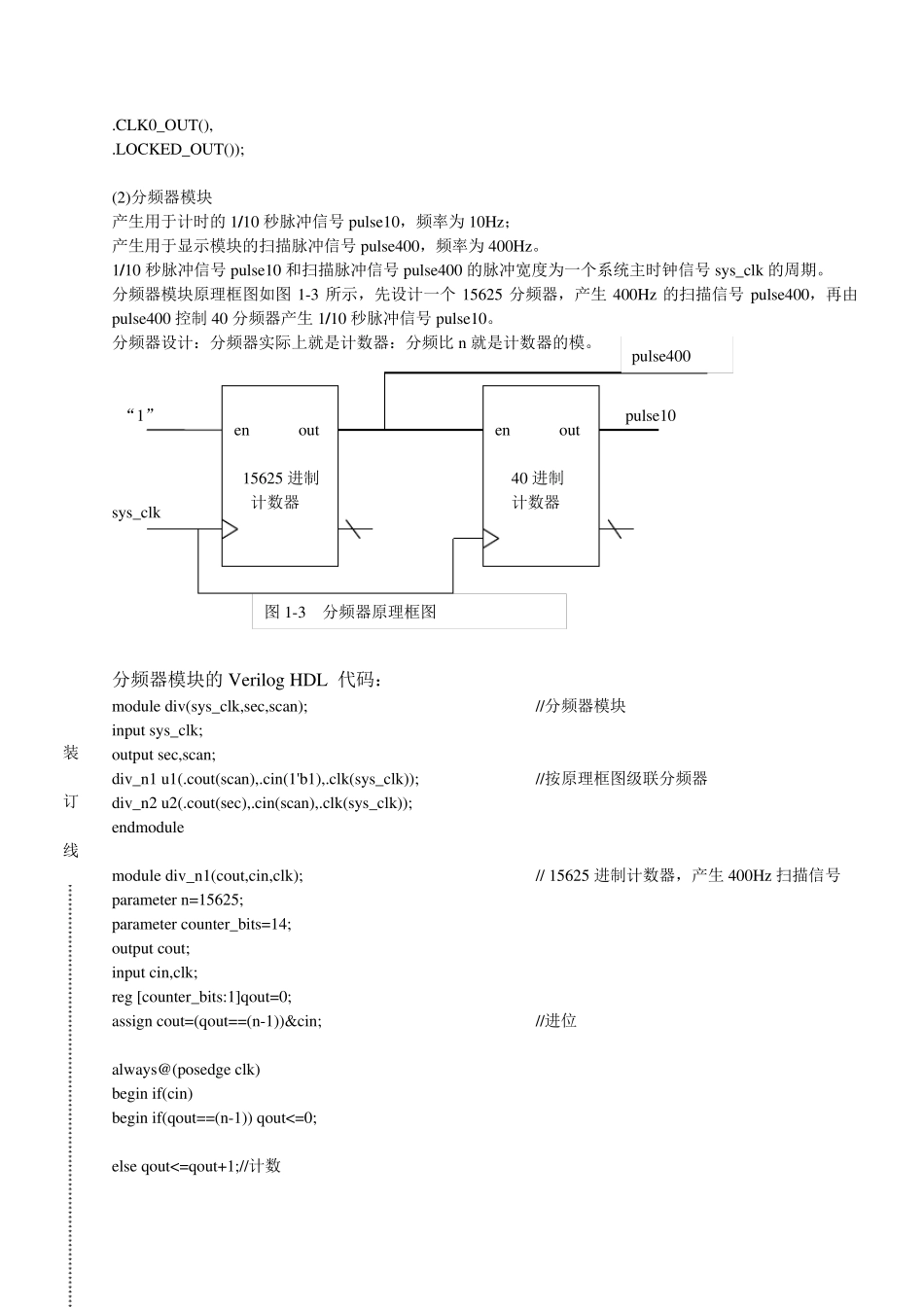

LOCKED_OUT()); (2)分频器模块 产生用于计时的1/10 秒脉冲信号pulse10,频率为10Hz; 产