第七章作业答案 7

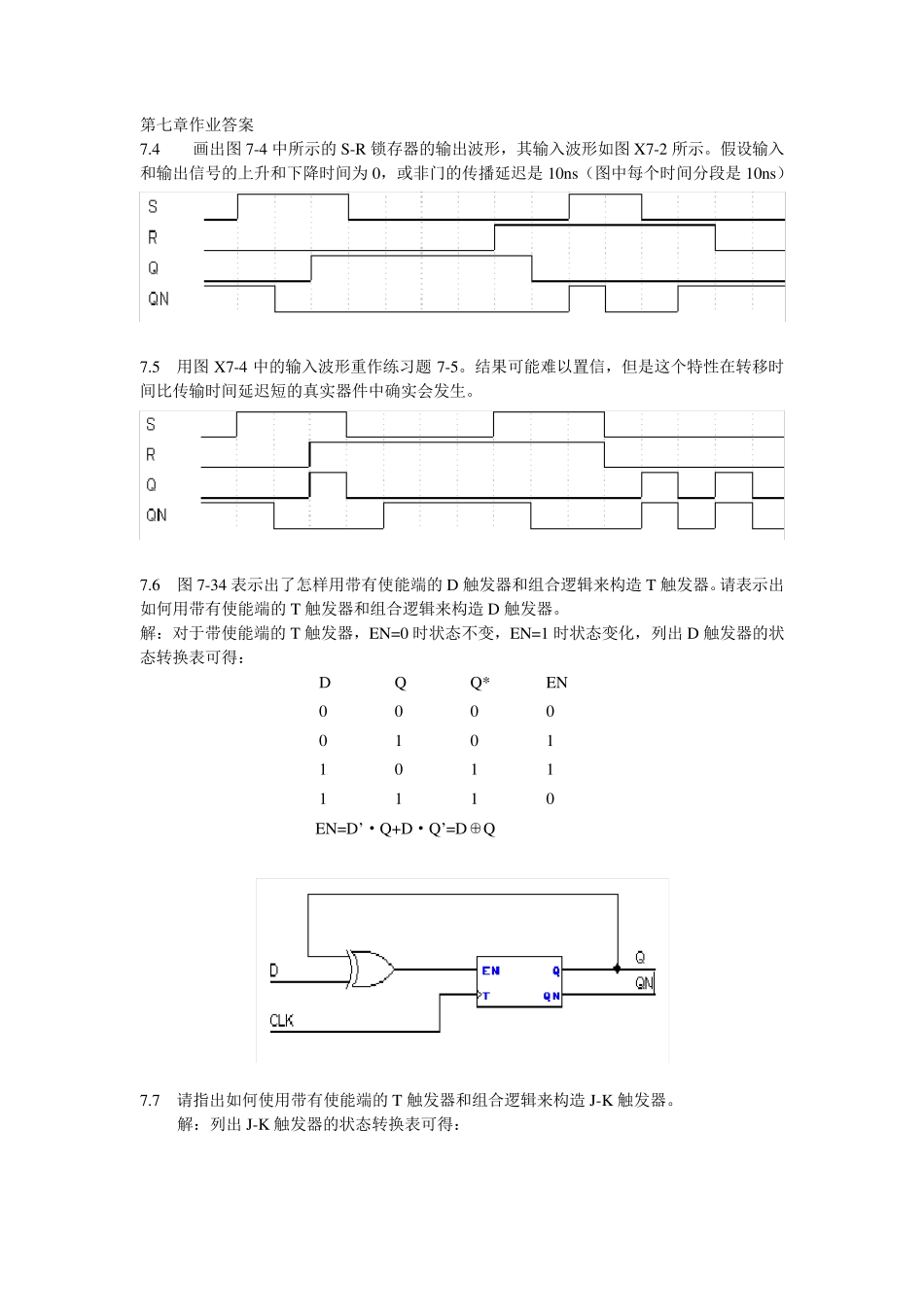

4 画出图7-4 中所示的S-R 锁存器的输出波形,其输入波形如图X7-2 所示

假设输入和输出信号的上升和下降时间为0,或非门的传播延迟是10ns(图中每个时间分段是10ns) 7

5 用图X7-4 中的输入波形重作练习题7-5

结果可能难以置信,但是这个特性在转移时间比传输时间延迟短的真实器件中确实会发生

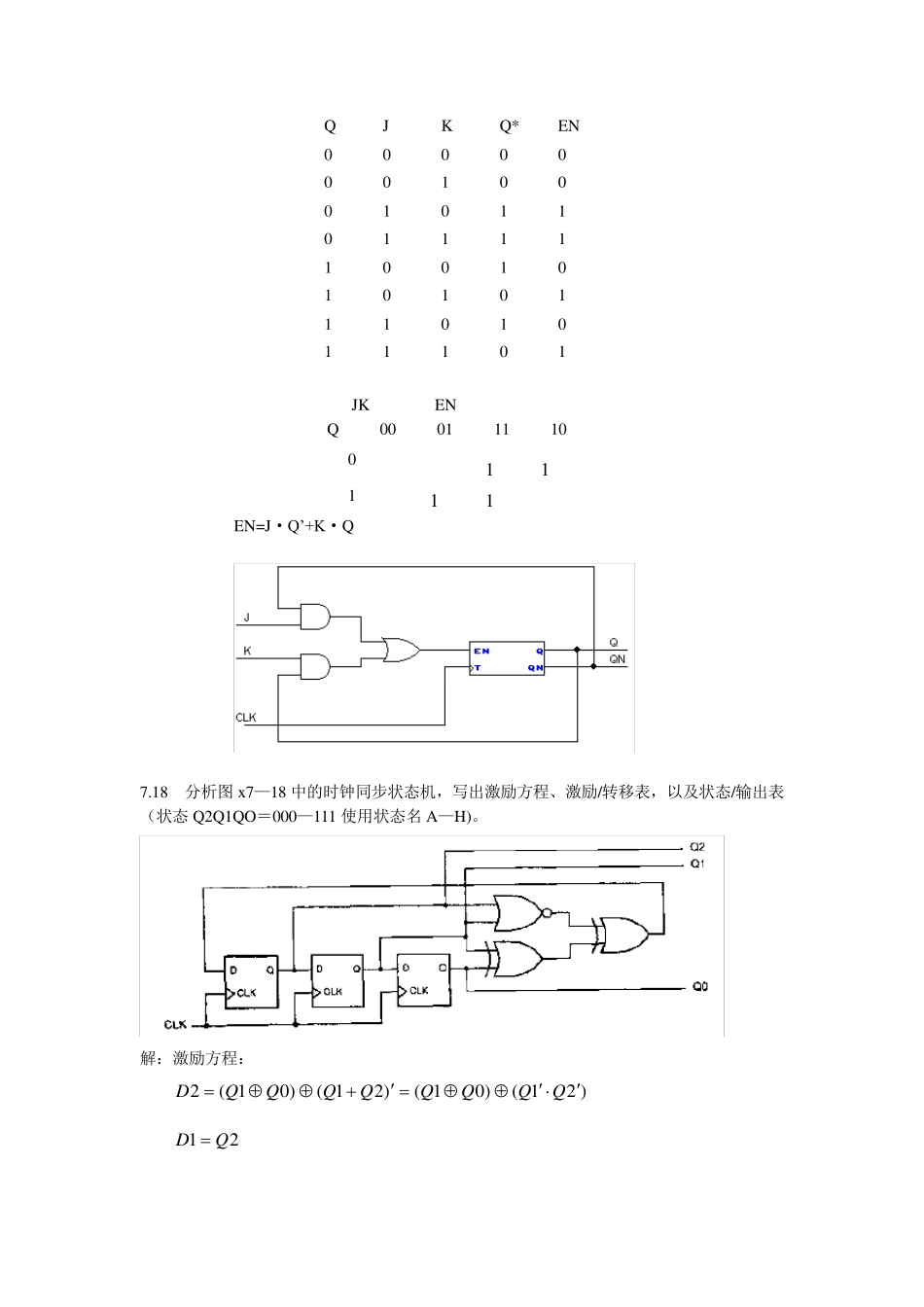

6 图7-34 表示出了怎样用带有使能端的D 触发器和组合逻辑来构造T 触发器

请表示出如何用带有使能端的T 触发器和组合逻辑来构造D 触发器

解:对于带使能端的T 触发器,EN=0 时状态不变,EN=1 时状态变化,列出D 触发器的状态转换表可得: D Q Q* EN 0 0 0 0 0 1 0 1 1 0 1 1 1 1 1 0 EN=D’·Q+D·Q’=D⊕Q 7

7 请指出如何使用带有使能端的T 触发器和组合逻辑来构造J-K 触发器

解:列出J-K 触发器的状态转换表可得: Q J K Q* EN 0 0 0 0 0 0 0 1 0 0 0 1 0 1 1 0 1 1 1 1 1 0 0 1 0 1 0 1 0 1 1 1 0 1 0 1 1 1 0 1 JK EN Q 00 01 11 10 0 1 EN=J·Q’+K·Q 7

18 分析图 x7—18 中的时钟同步状态机,写出激励方程、激励/转移表,以及状态/输出表 (状态 Q2Q1QO=000—111 使用状态名 A—H)

解:激励方程: )21()01()21()01(2QQQQQQQQD 21QD 1 1 1 1 XY Q1Q2 00 01 10 11 00 00 10 00 10 01 00 10 00 10 10 00 11 00 10 11 00 11 00 10 EN1EN2 XY Q1Q2 00 01 10 11 00 00,1 10