通信原理实验报告 数字锁相环实验 姓名: 学号: 实验2 数字锁相环实验 一、实验原理和电路说明 在电信网中,同步是一个十分重要的概念

同步的种类很多,有时钟同步、比特同步等等,其最终目的使本地终端时钟源锁定在另一个参考时钟源上,如果所有的终端均采用这种方式,则所有终端将以统一步调进行工作

同步的技术基础是锁相,因而锁相技术是通信中最重要的技术之一

锁相环分为模拟锁相环与数字锁相环,本实验将对数字锁相环进行实验

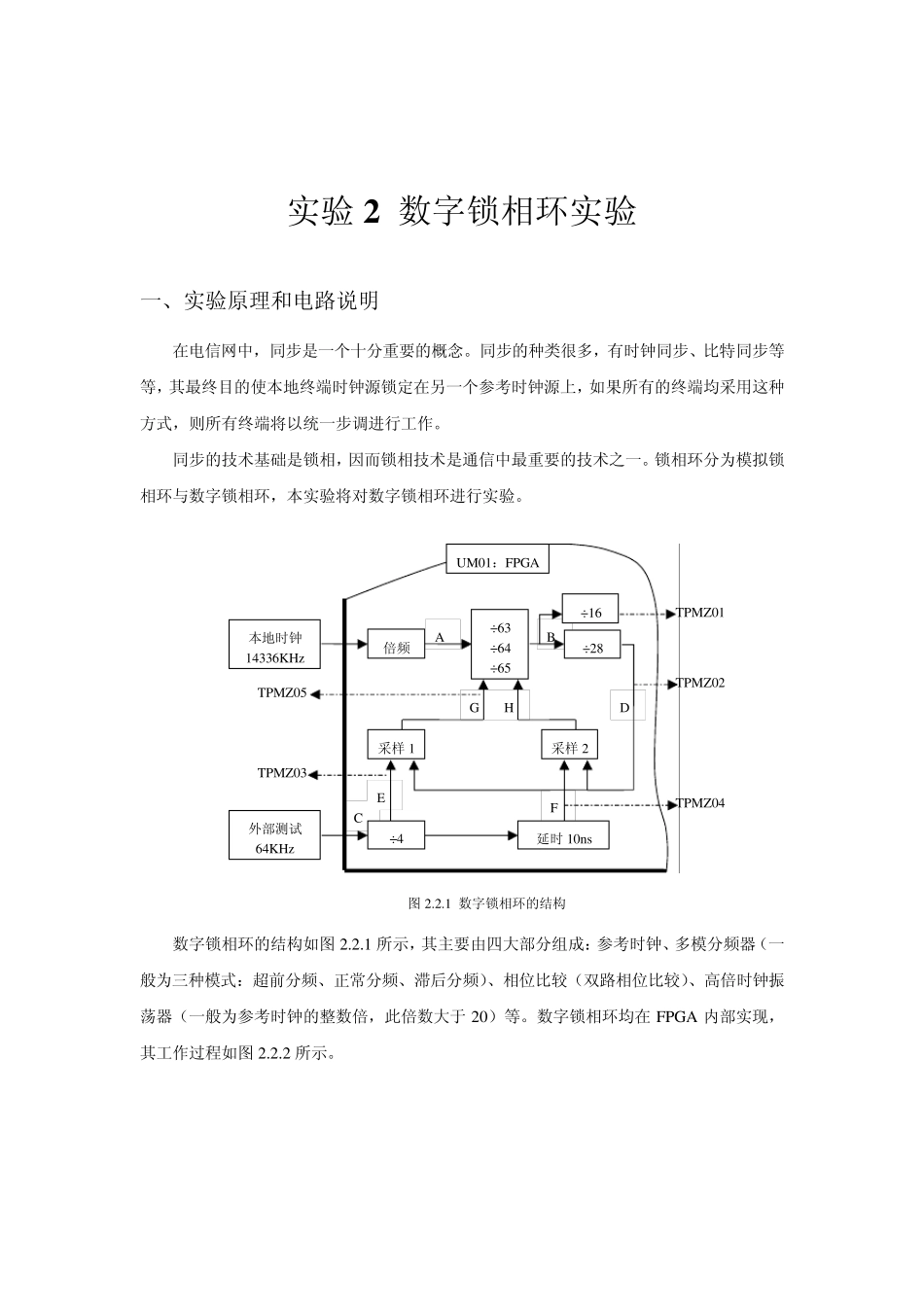

BCAHGFED本地时钟14336KHz外部测试64KHz倍频÷63÷64÷65÷28÷4延时 10ns采样 1采样 2UM01:FPGATPMZ03TPMZ05图 2

1 数字锁相环的结构TPMZ04TPMZ02÷16TPMZ01 数字锁相环的结构如图 2

1 所示,其主要由四大部分组成:参考时钟、多模分频器(一般为三种模式:超前分频、正常分频、滞后分频)、相位比较(双路相位比较)、高倍时钟振荡器(一般为参考时钟的整数倍,此倍数大于 20)等

数字锁相环均在 FPGA 内部实现,其工作过程如图 2

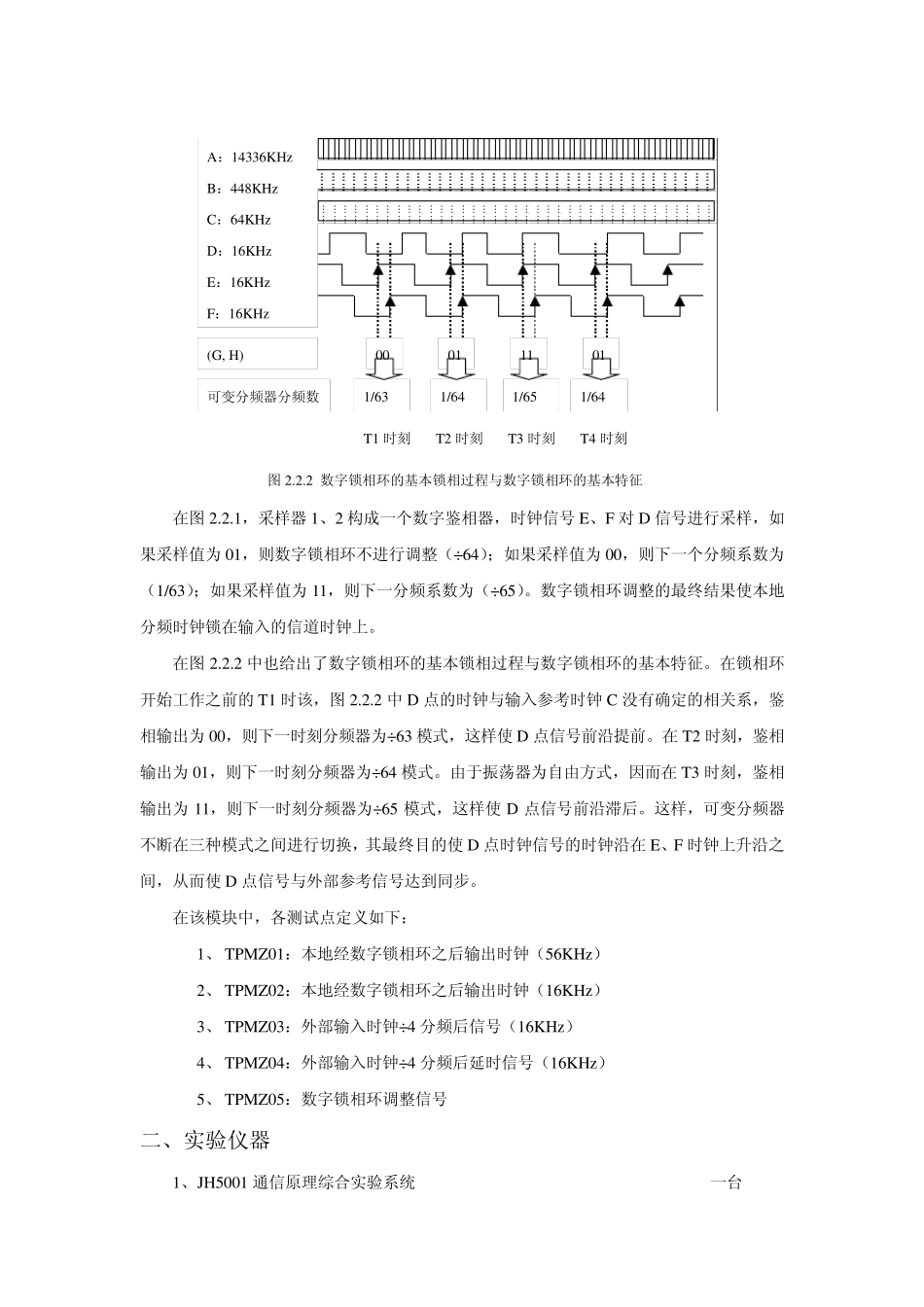

A:14336KHzB:448KHzC:64KHzE:16KHzF:16KHz000111011/631/641/651/64D:16KHz(G, H)可变分频器分频数T1 时刻T2 时刻T3 时刻T4 时刻图2

2 数字锁相环的基本锁相过程与数字锁相环的基本特征 在图2

1,采样器1、2 构成一个数字鉴相器,时钟信号 E、F 对 D 信号进行采样,如果采样值为 01,则数字锁相环不进行调整(÷64);如果采样值为 00,则下一个分频系数为(1/63);如果采样值为 11,则下一分频系数为(÷65)

数字锁相环调整的最终结果使本地分频时钟锁在输入的信道时钟上

2 中也给出了数字锁相环的基本锁相过程与数字锁相环的基本特征