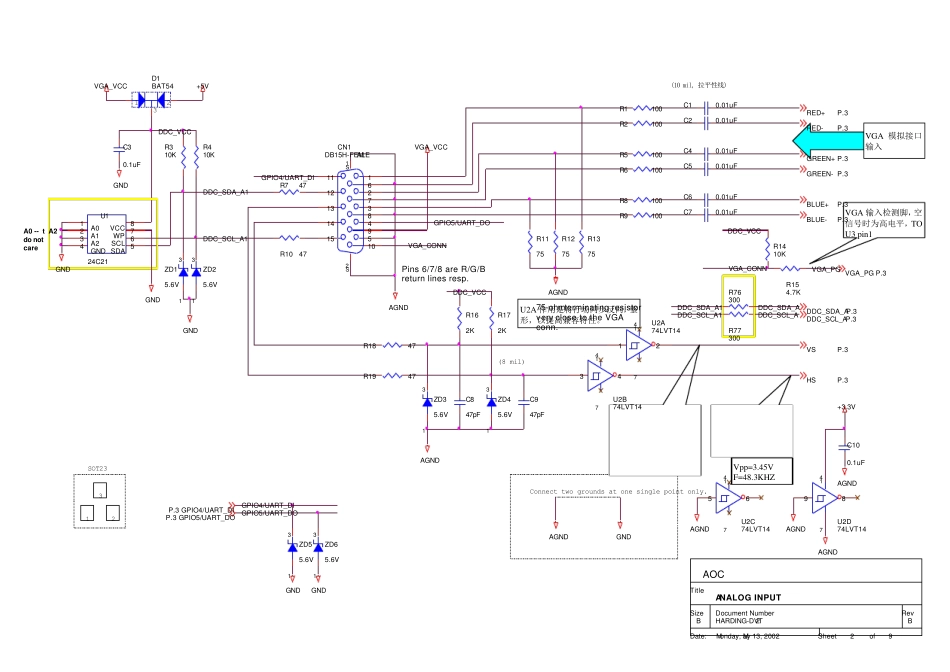

(10 mil, 拉平性线)AGNDDDC_SCL_A1R1100GPIO4/UART_DISOT23VGA_CONNCN1DB15H-FEMALE162738495111213141510S1S2ZD55.6V13C40.01uFVGA_VCCGPIO4/UART_DIU2B74LVT1434147R1375C50.01uFR77300VGA_PG P.3R9100GREEN- P.33GPIO5/UART_DOP.3R6100U2D74LVT1498147AGNDBLUE+P.3C947pFZD25.6V13GNDDDC_SDA_A1R1410KGNDGREEN+ P.375-ohm terminating resistorvery close to the VGAconn.VGA_CONNR8100R1275AGNDAGNDR1175AGNDC10.01uFR1047HARDING-DVT2BANALOG INPUTAOCB29Monday, May 13, 2002TitleSizeDocument NumberRevDate:SheetofRED-P.3R310KGPIO4/UART_DIP.31VSP.3DDC_SDA_AP.3HSP.3RED+P.3R747C20.01uFU2C74LVT1456147R154.7KZD65.6V13GPIO5/UART_DODDC_VCCA0 --> A2 do notcareGNDGNDR76300C70.01uFU124C2148123765GNDVCCA0A1A2WPSCLSDAZD45.6V13123D1BAT54DDC_SCL_AP.3C847pFC30.1uFAGNDPins 6/7/8 are R/G/Breturn lines resp.AGNDBLUE-P.3VGA_PGR1847AGND(8 mil)DDC_VCCDDC_SCL_AZD35.6V13C60.01uFR162K+3.3VGNDDDC_SDA_AConnect two grounds at one single point only.R1947R2100R5100ZD15.6V13C100.1uFGND+5VVGA_VCCDDC_SDA_A1GPIO5/UART_DOU2A74LVT1412147DDC_VCC2DDC_SCL_A1R410KR172KGND Vp p =3.45V F=48.3KHZ U2A 作用是将行场同步反向,整形,以提高兼容特性。 VGA 输入检测脚,空信号时为高电平,TO U3 p in 1 VGA 模拟接口输入 RCL KP.4EG7R391 0KC210 .1u FF B6GPIO(22:16) is on "H ost P ort" pinsOCM_STAR TRM ADDR0C160 .1u F+ 5V+ 2.5 VL ED_GRNP.4DDC_SCL_AP.2RM DAT A3GPIO3R361 0KGNDER7GNDBLUE+P.2GPIO5/ UART _DO P.2EB2R291 K0 = X TAL and TCLK pins are connectedGNDSCLC130 .1u FR28Bea d 1 20+ 5VGPIO2P.4R26Bea d 1 20F B3GNDRM DAT A3T CON_ EINV+C301 0u FxBLUE-P.2SDARM ADDR1 5C150 .1u FROM_AD DR(12:10)GNDVGA_PGP.2RP11 20 oh m be ad12345678R254 .7KOR0F B2GNDOR4+C314 7u FC12 3NCIf us ing 6-wire host protoc ol, program this bit to 0OR5OG1EB1RM DAT A12 .5V_RXPLER2EB0C13 02 2p FC270 .1u F1 = OCM becomes ac tiv e after O CM_CLK is stableOR[0 ..7 ]P.4GPIO6P.4RM DAT A71 = A ll 48K of ROM is in ex ternal R OMEB4BOOTST...