第四章1.一个容量为 16K×32 位的存储器,其地址线和数据线的总和是多少

当选用下列不同规格的存储芯片时,各需要多少片

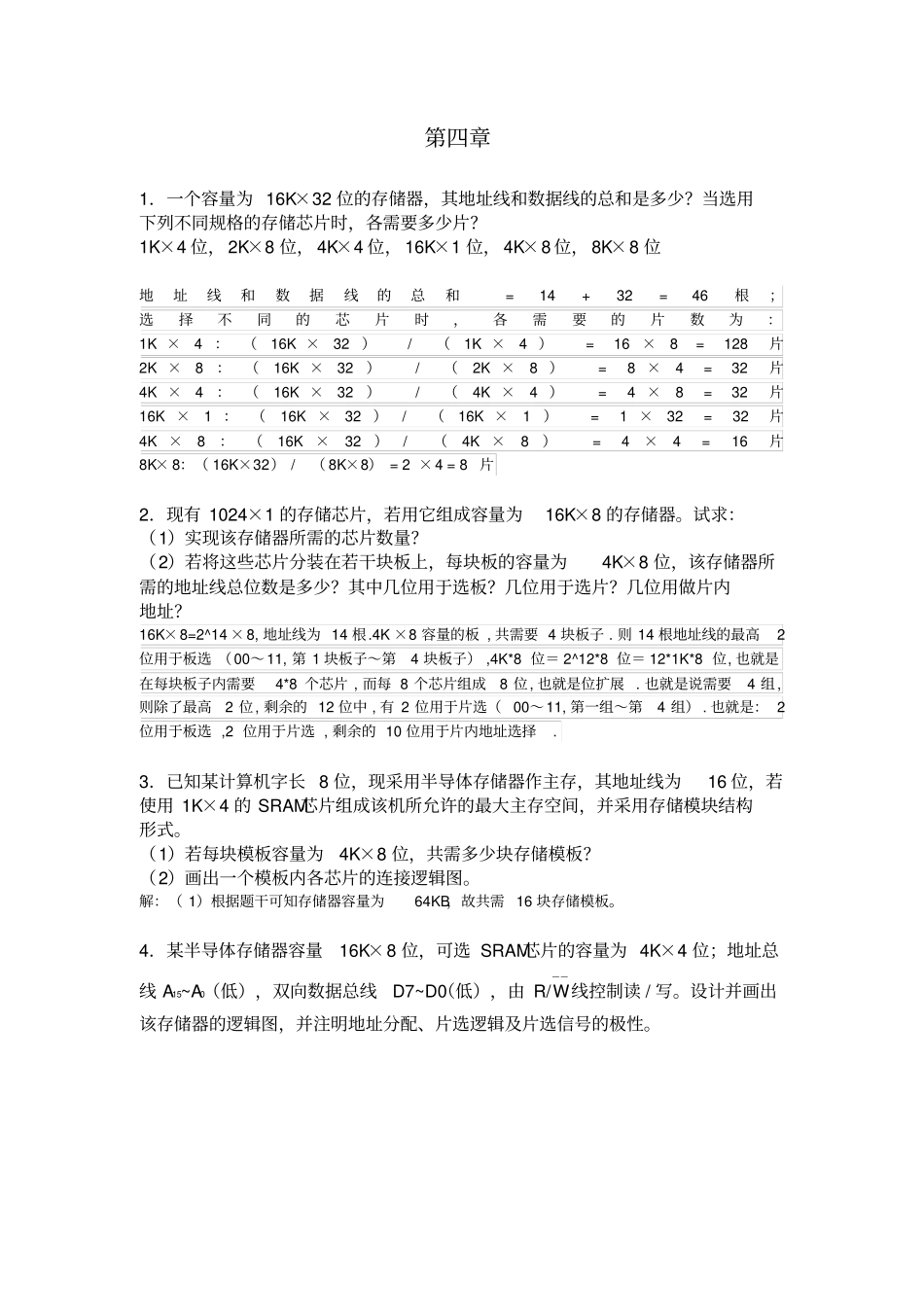

1K×4 位, 2K×8 位, 4K×4 位, 16K×1 位, 4K×8 位, 8K×8 位地址线和数据线的总和= 14 + 32 = 46根;选择不同的芯片时,各需要的片数为:1K ×4:(16K ×32)/ (1K ×4 )= 16×8 = 128片2K ×8:(16K ×32)/ (2K ×8 )= 8 ×4 = 32片4K ×4:(16K ×32)/ (4K ×4 )= 4 ×8 = 32片16K ×1 :(16K ×32)/ (16K ×1)= 1 ×32 = 32片4K ×8:(16K×32)/ (4K ×8)= 4×4 = 16片8K× 8:( 16K×32) / ( 8K×8) = 2 ×4 = 8片2.现有 1024×1 的存储芯片,若用它组成容量为16K×8 的存储器

试求:(1)实现该存储器所需的芯片数量

(2)若将这些芯片分装在若干块板上,每块板的容量为4K×8 位,该存储器所需的地址线总位数是多少

其中几位用于选板

几位用于选片

几位用做片内地址

16K×8=2^14 ×8, 地址线为 14 根

4K ×8 容量的板 , 共需要 4 块板子

则 14 根地址线的最高2位用于板选 (00~11, 第 1 块板子~第4 块板子) ,4K*8 位= 2^12*8 位= 12*1K*8 位, 也就是在每块板子内需要4*8 个芯片 , 而每 8 个芯片组成8 位, 也就是位扩展

也就是说需要4 组,则除了最高2 位, 剩余的 12 位中 , 有 2 位用于片选( 00~11, 第一组~第4 组)

也就是: 2位用于板选 ,2 位用于片选 , 剩余的 10 位用于片内地址选择

3.已知某计算机字长 8 位,现采用半导体存储器