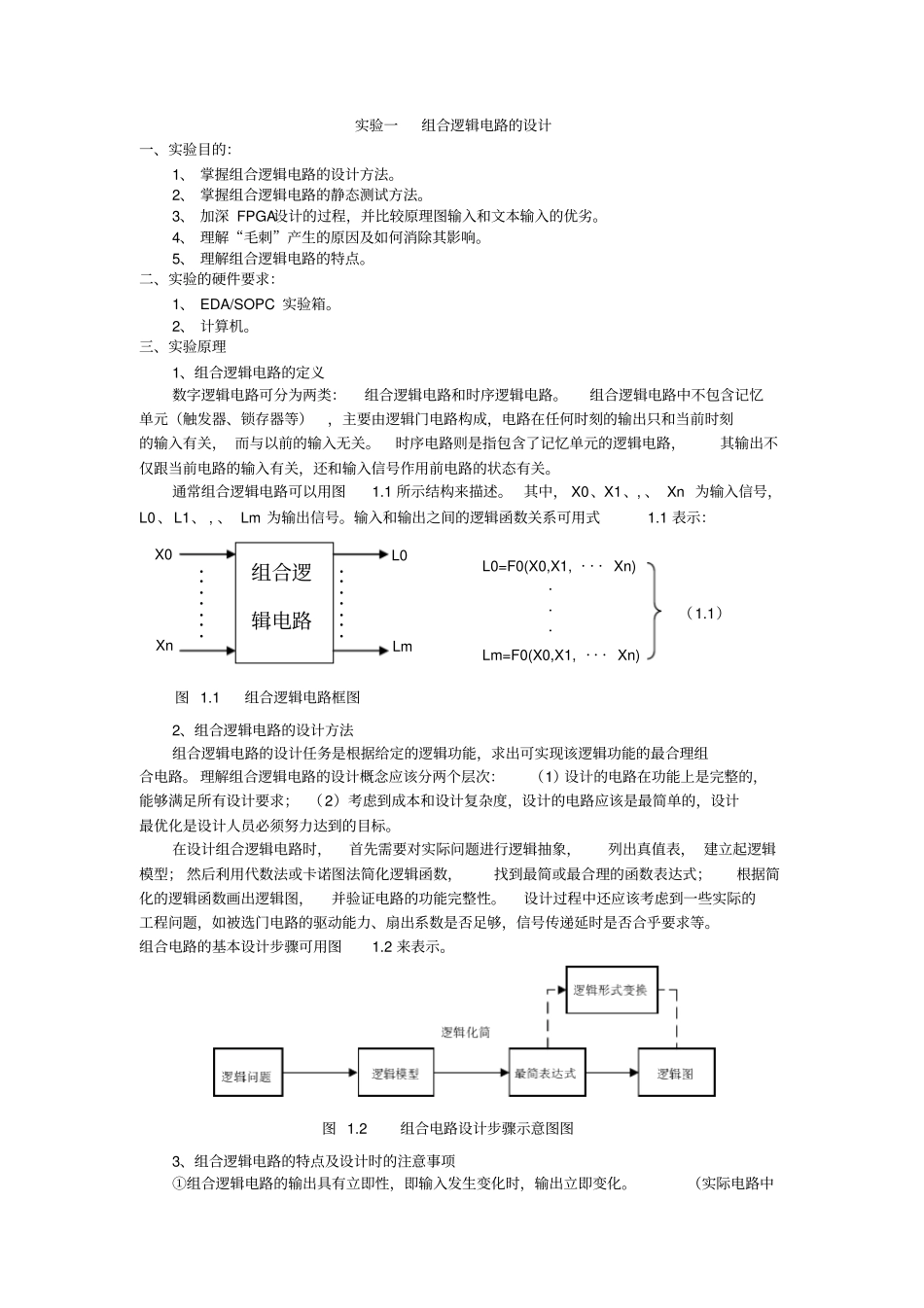

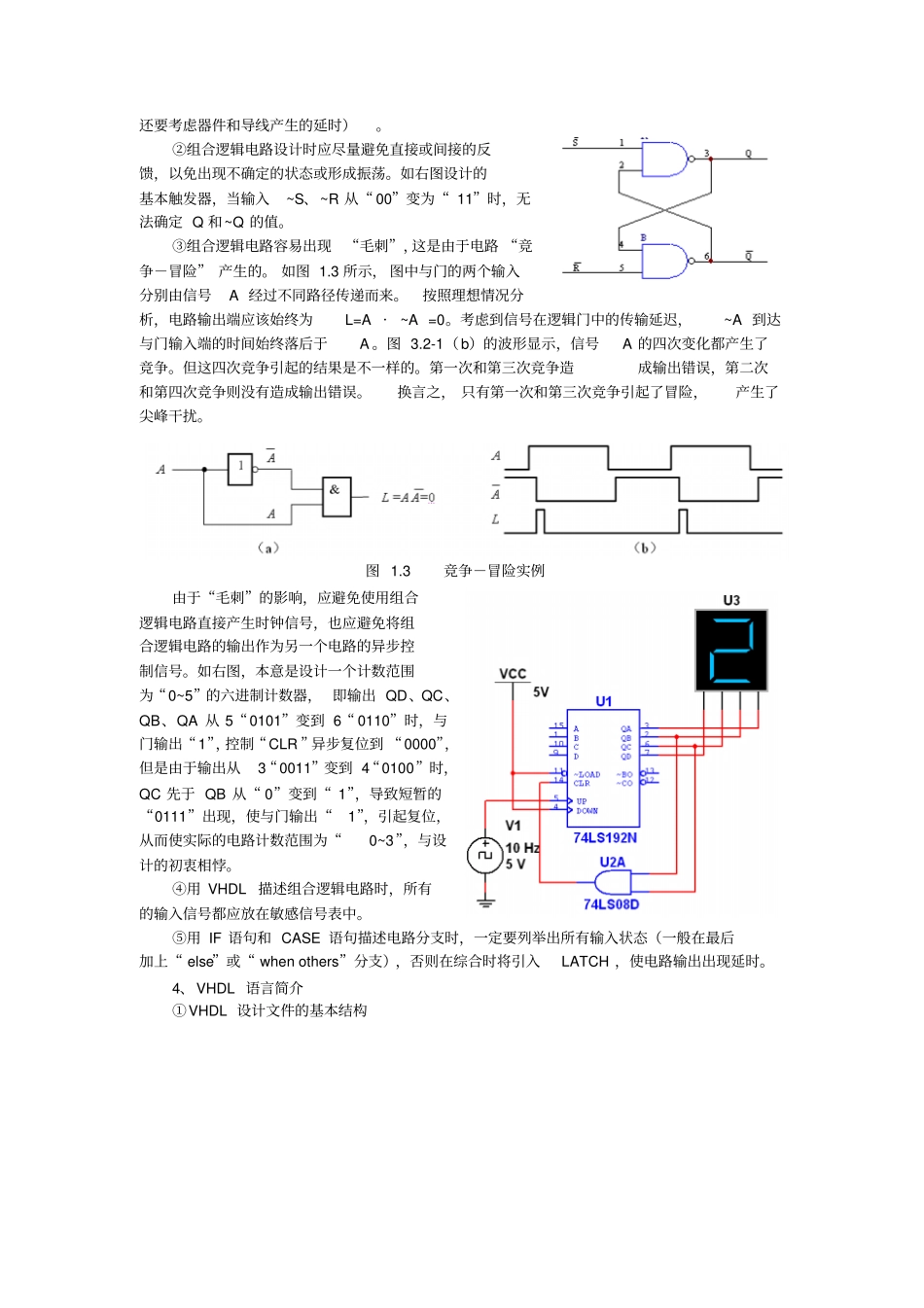

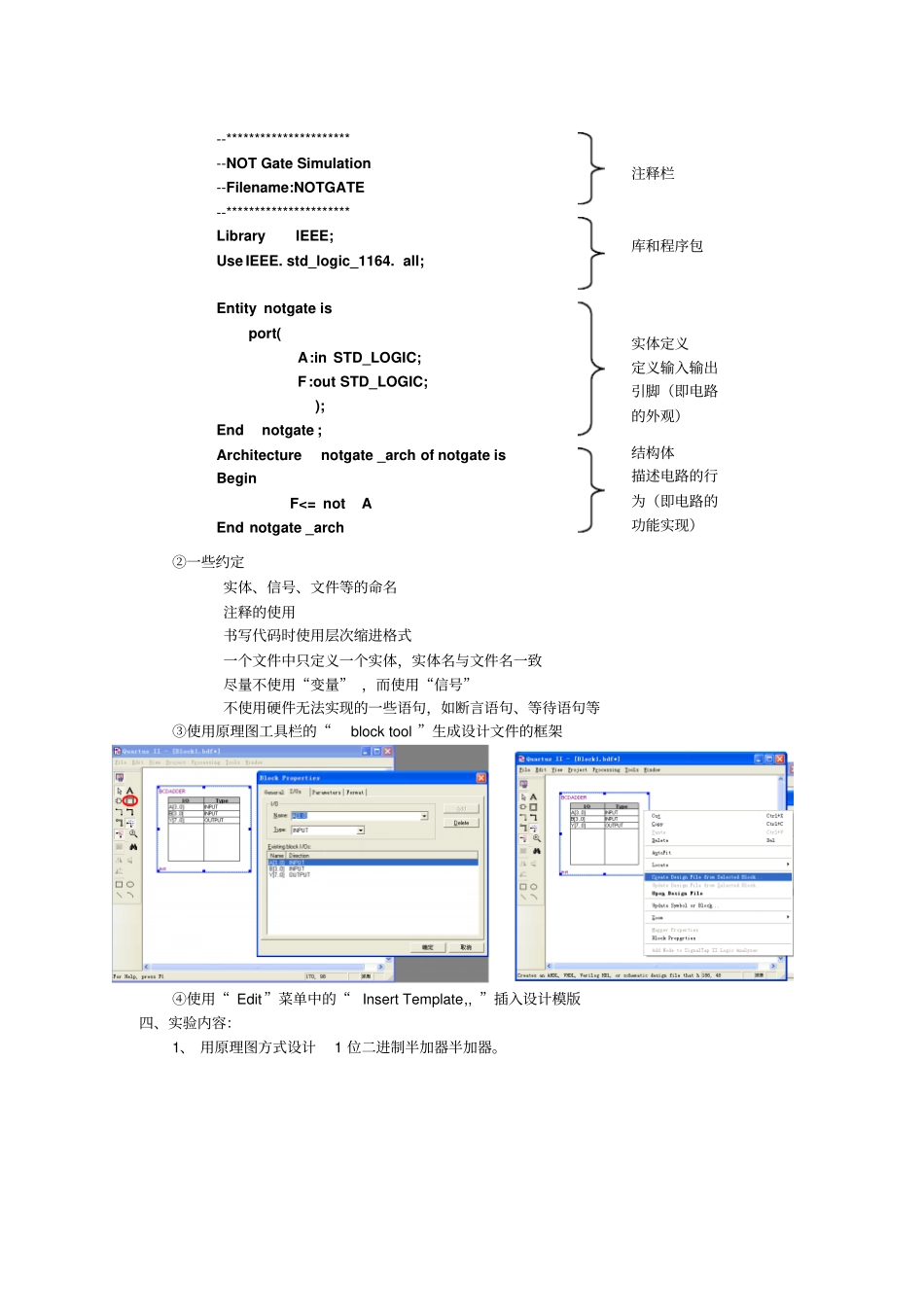

实验一组合逻辑电路的设计一、实验目的:1、 掌握组合逻辑电路的设计方法。2、 掌握组合逻辑电路的静态测试方法。3、 加深 FPGA设计的过程,并比较原理图输入和文本输入的优劣。4、 理解“毛刺”产生的原因及如何消除其影响。5、 理解组合逻辑电路的特点。二、实验的硬件要求:1、 EDA/SOPC 实验箱。2、 计算机。三、实验原理1、组合逻辑电路的定义数字逻辑电路可分为两类:组合逻辑电路和时序逻辑电路。组合逻辑电路中不包含记忆单元(触发器、锁存器等),主要由逻辑门电路构成,电路在任何时刻的输出只和当前时刻的输入有关, 而与以前的输入无关。时序电路则是指包含了记忆单元的逻辑电路,其输出不仅跟当前电路的输入有关,还和输入信号作用前电路的状态有关。通常组合逻辑电路可以用图1.1 所示结构来描述。 其中, X0、X1、, 、 Xn 为输入信号,L0 、L1、 , 、 Lm 为输出信号。输入和输出之间的逻辑函数关系可用式1.1 表示:2、组合逻辑电路的设计方法组合逻辑电路的设计任务是根据给定的逻辑功能,求出可实现该逻辑功能的最合理组合电路。 理解组合逻辑电路的设计概念应该分两个层次:(1)设计的电路在功能上是完整的,能够满足所有设计要求; (2)考虑到成本和设计复杂度,设计的电路应该是最简单的,设计最优化是设计人员必须努力达到的目标。在设计组合逻辑电路时,首先需要对实际问题进行逻辑抽象,列出真值表, 建立起逻辑模型; 然后利用代数法或卡诺图法简化逻辑函数,找到最简或最合理的函数表达式;根据简化的逻辑函数画出逻辑图,并验证电路的功能完整性。设计过程中还应该考虑到一些实际的工程问题,如被选门电路的驱动能力、扇出系数是否足够,信号传递延时是否合乎要求等。组合电路的基本设计步骤可用图1.2 来表示。3、组合逻辑电路的特点及设计时的注意事项①组合逻辑电路的输出具有立即性,即输入发生变化时,输出立即变化。(实际电路中组合逻辑电路··············X0 Xn L0 Lm 图 1.1 组合逻辑电路框图L0=F0(X0,X1, · · · Xn) ···Lm=F0(X0,X1, · · · Xn) (1.1)图 1.2 组合电路设计步骤示意图图还要考虑器件和导线产生的延时)。②组合逻辑电路设计时应尽量避免直接或间接的反馈,以免出现不确定的状态或形成振荡。如右图设计的基本触发器,当输入~S、~R 从“ 00”变为“ 11”时,无法确定 Q 和~Q 的值。③组合逻辑电路容易出现“毛刺”,这...