实验一: 设计输入与门级结构建模仿真一、实验目的:1、掌握简单门级结构建模电路的设计方法

2、初步掌握 ModelSim6

0 软件的基本操作与应用

3、初步了解 verilog 建模仿真的设计全过程

二、实验设备:PC 机一台ModelSim6

0 开发软件三、试验要求:设计输入(2 学时)学习使用 ModelSim6

0 设计软件

学习文本编辑器使用, 掌握文本编辑器的输入方法,完成本讲实例门级2 选 1 多路选择器结构建模的输入和门级2 位全加器器结构建模的输入,并完成仿真

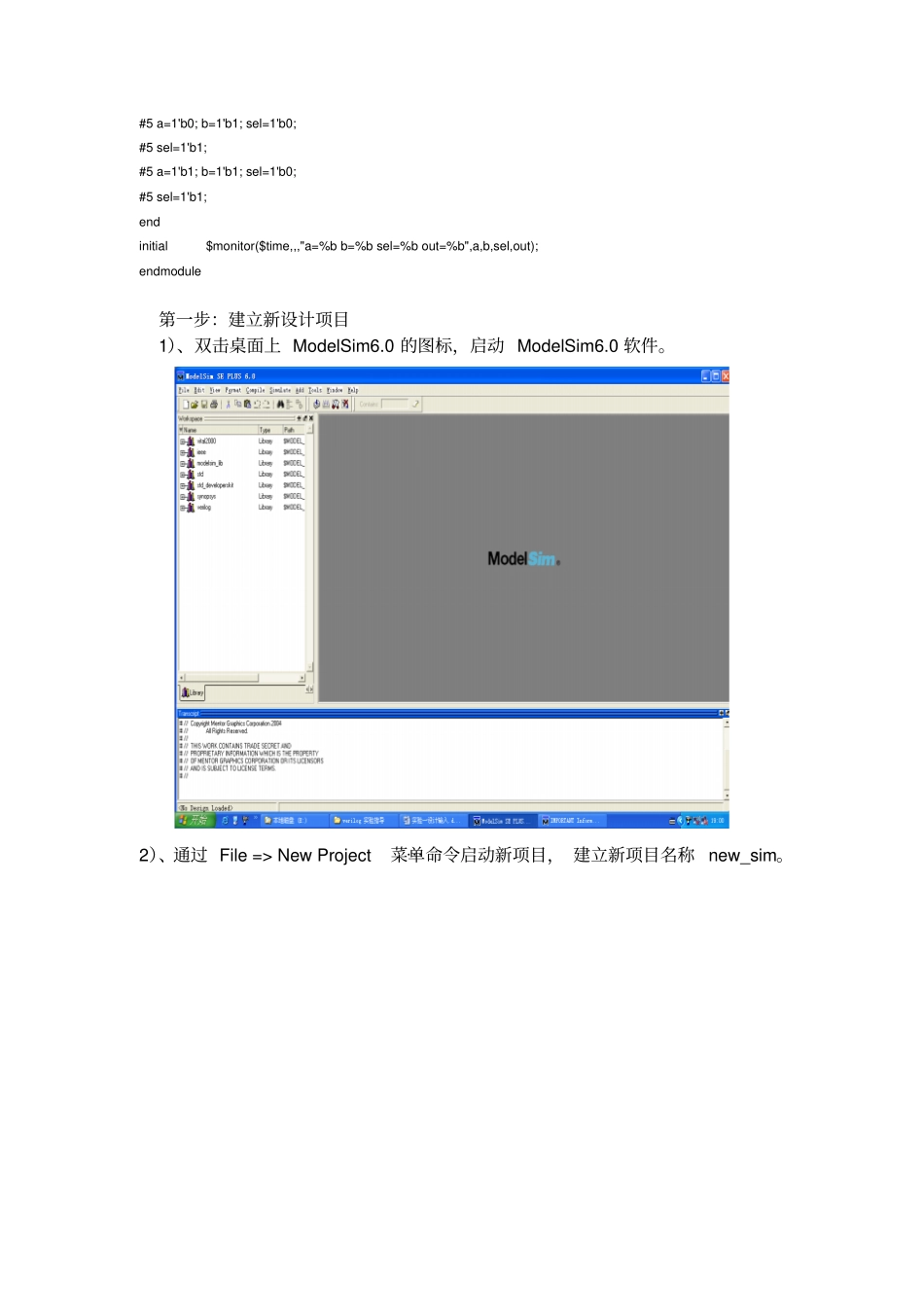

四、实验步骤:ModelSim6

0 设计输入ModelSim6

0以下内容为程序代码 :门级结构描述的2 选1MUX module user_mux(out,a,b,sel); output out; input a,b,sel; not (sel_,sel); and (a1,a,sel_), (a2,b,sel); or (out,a1,a2); endmodule2 选 1 多路选择器的仿真`timescale 1ns/1ns module mux_tp; reg a,b,sel; wire out;user_mux m1(out,a,b,sel); //调用待测试模块initial begin a=1'b0; b=1'b0; sel=1'b0; #5 sel=1'b1; #5 a=1'b1; sel=1'b0; #5 sel=1'b1; #5 a=1'b0; b=1'b1; sel=1'b0; #5 sel=1'b1; #5 a=1'b1; b=1'b1; sel=1'b0; #5 sel=1'b1; end initial $monit