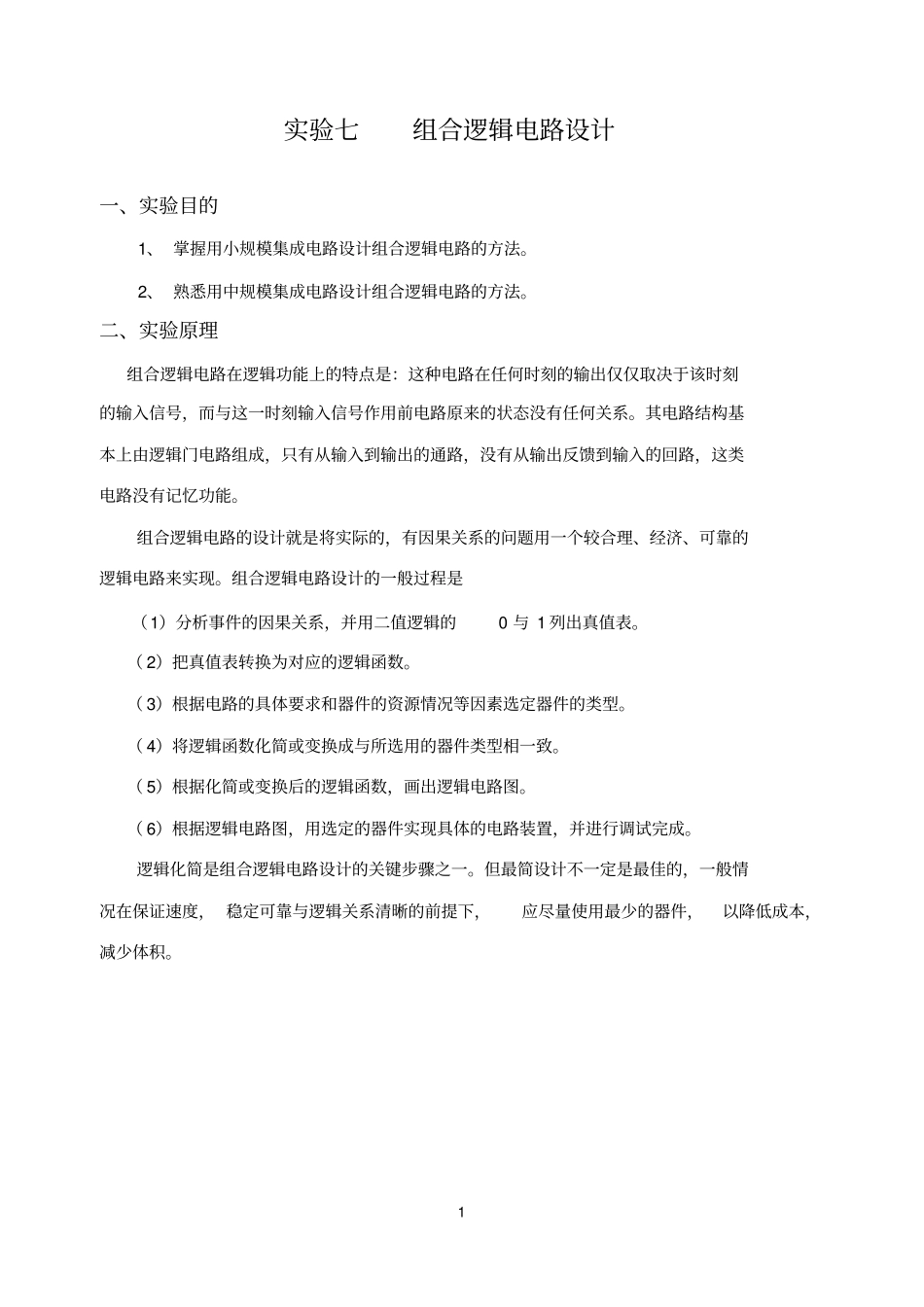

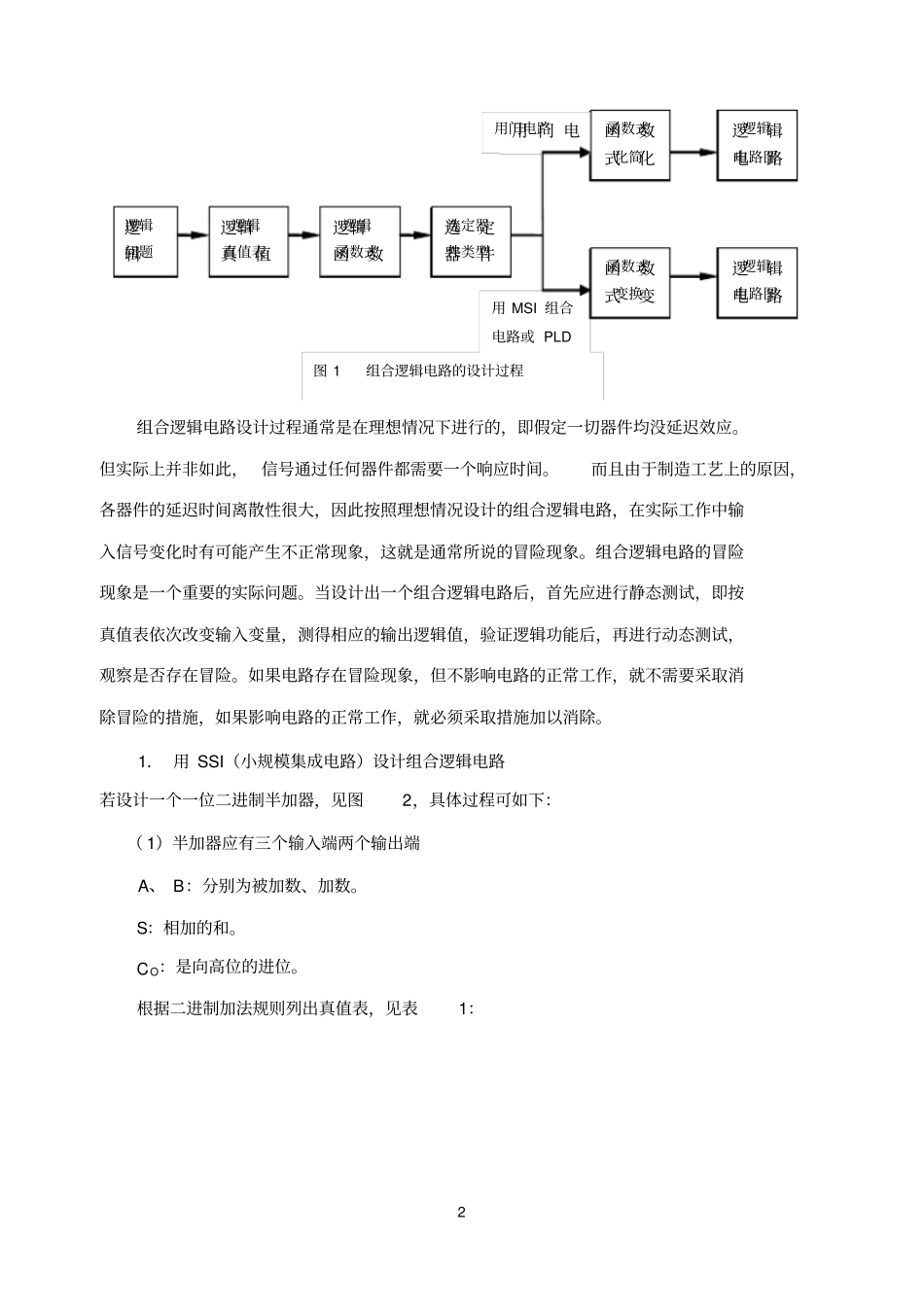

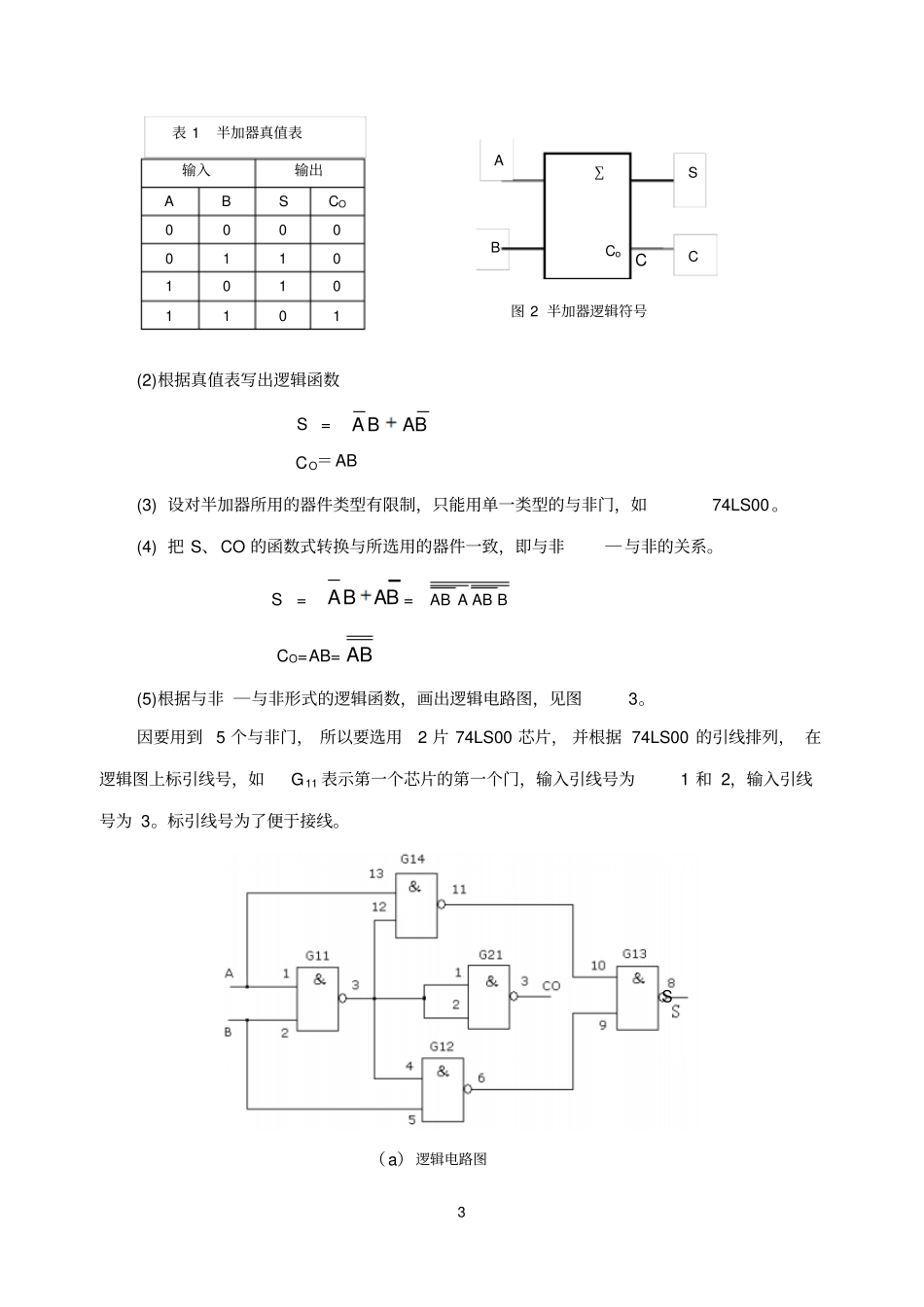

1 实验七组合逻辑电路设计一、实验目的1、 掌握用小规模集成电路设计组合逻辑电路的方法。2、 熟悉用中规模集成电路设计组合逻辑电路的方法。二、实验原理组合逻辑电路在逻辑功能上的特点是:这种电路在任何时刻的输出仅仅取决于该时刻的输入信号,而与这一时刻输入信号作用前电路原来的状态没有任何关系。其电路结构基本上由逻辑门电路组成,只有从输入到输出的通路,没有从输出反馈到输入的回路,这类电路没有记忆功能。组合逻辑电路的设计就是将实际的,有因果关系的问题用一个较合理、经济、可靠的逻辑电路来实现。组合逻辑电路设计的一般过程是(1)分析事件的因果关系,并用二值逻辑的0 与 1 列出真值表。( 2)把真值表转换为对应的逻辑函数。( 3)根据电路的具体要求和器件的资源情况等因素选定器件的类型。( 4)将逻辑函数化简或变换成与所选用的器件类型相一致。( 5)根据化简或变换后的逻辑函数,画出逻辑电路图。( 6)根据逻辑电路图,用选定的器件实现具体的电路装置,并进行调试完成。逻辑化简是组合逻辑电路设计的关键步骤之一。但最简设计不一定是最佳的,一般情况在保证速度, 稳定可靠与逻辑关系清晰的前提下,应尽量使用最少的器件,以降低成本,减少体积。2 组合逻辑电路设计过程通常是在理想情况下进行的,即假定一切器件均没延迟效应。但实际上并非如此, 信号通过任何器件都需要一个响应时间。而且由于制造工艺上的原因,各器件的延迟时间离散性很大,因此按照理想情况设计的组合逻辑电路,在实际工作中输入信号变化时有可能产生不正常现象,这就是通常所说的冒险现象。组合逻辑电路的冒险现象是一个重要的实际问题。当设计出一个组合逻辑电路后,首先应进行静态测试,即按真值表依次改变输入变量,测得相应的输出逻辑值,验证逻辑功能后,再进行动态测试,观察是否存在冒险。如果电路存在冒险现象,但不影响电路的正常工作,就不需要采取消除冒险的措施,如果影响电路的正常工作,就必须采取措施加以消除。1. 用 SSI(小规模集成电路)设计组合逻辑电路若设计一个一位二进制半加器,见图2,具体过程可如下:( 1)半加器应有三个输入端两个输出端A、 B:分别为被加数、加数。S:相加的和。CO:是向高位的进位。根据二进制加法规则列出真值表,见表1:函数式化逻辑电路用 门 电用 MSI 组合电路或 PLD 用门电路逻辑逻辑真值逻辑函数选定器件函数式变逻辑电路图 1 组合逻辑电路的设计过程逻辑...