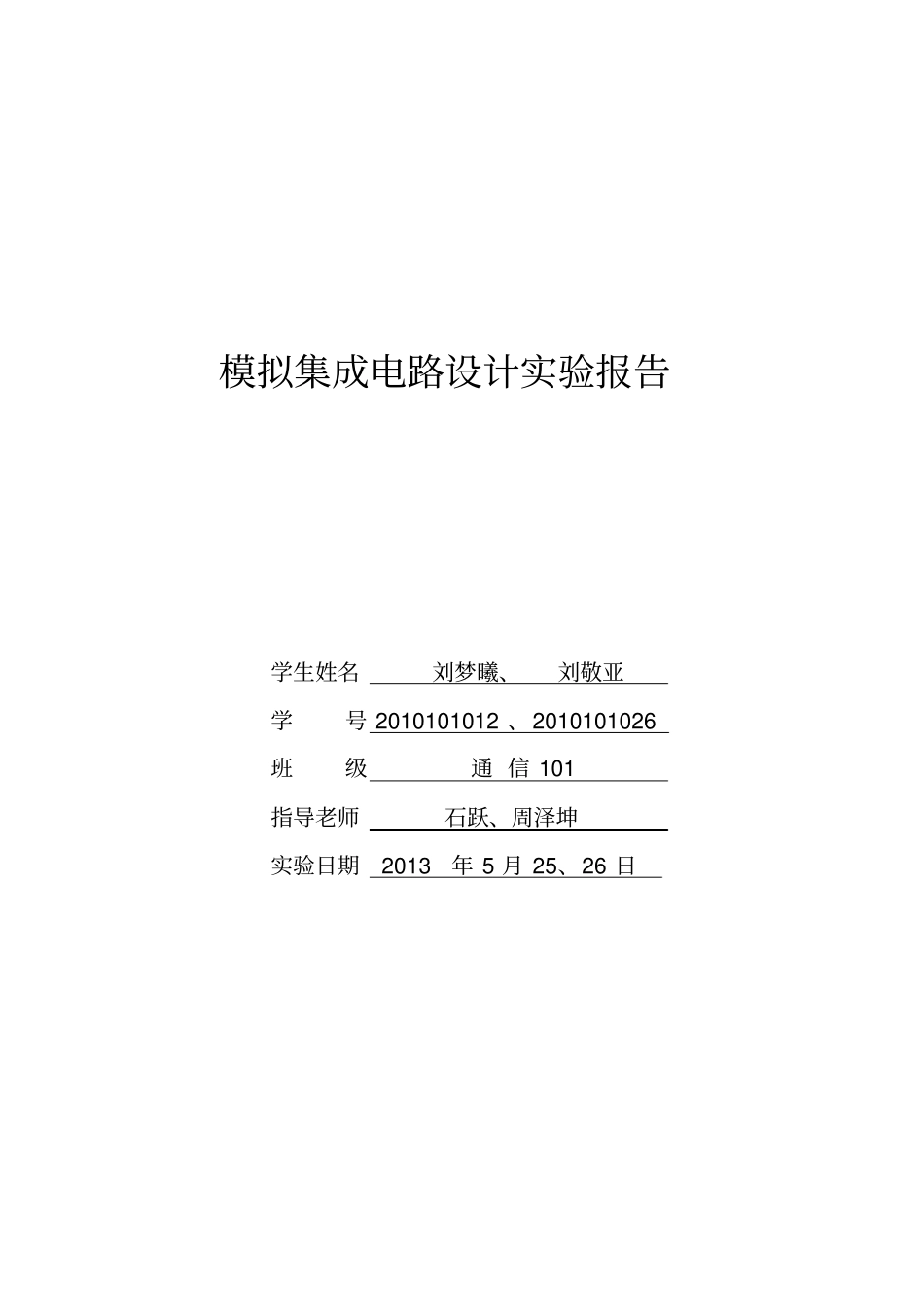

模拟集成电路设计实验报告学生姓名刘梦曦、刘敬亚学号 2010101012 、2010101026 班级通 信 101 指导老师石跃、周泽坤实验日期 2013年 5 月 25、26 日实验二: CMOS模拟集成电路设计与仿真一、实验步骤1、进入虚拟机下的Cadence(虚拟机下 linux用户名:xcx 密码:000000)Cadence运行方法:在 linux 桌面右键选择新建终端——>在终端输入 cd tsmc0_18rfp4_v15 回车—— >输入 lmli 回车—— >输入 icfb& 回车2、在 CIW(command Interpreter window)命令框中,点击 Tools —— > Library Manager,出现 LM(Library Manager )窗口建立一个新的 Library :点击 File —— >New—— >Library ,出现 New Library窗口;填入 Library的名称,点击 OK 出现 Load Technology 窗口,添加工艺文件:选择analogLib ,依次选择和添加所需要的器件, 并且按照下图连接起来, 并根据要求修改它们的参数,再保存,一个完整的电路拓扑图就形成了

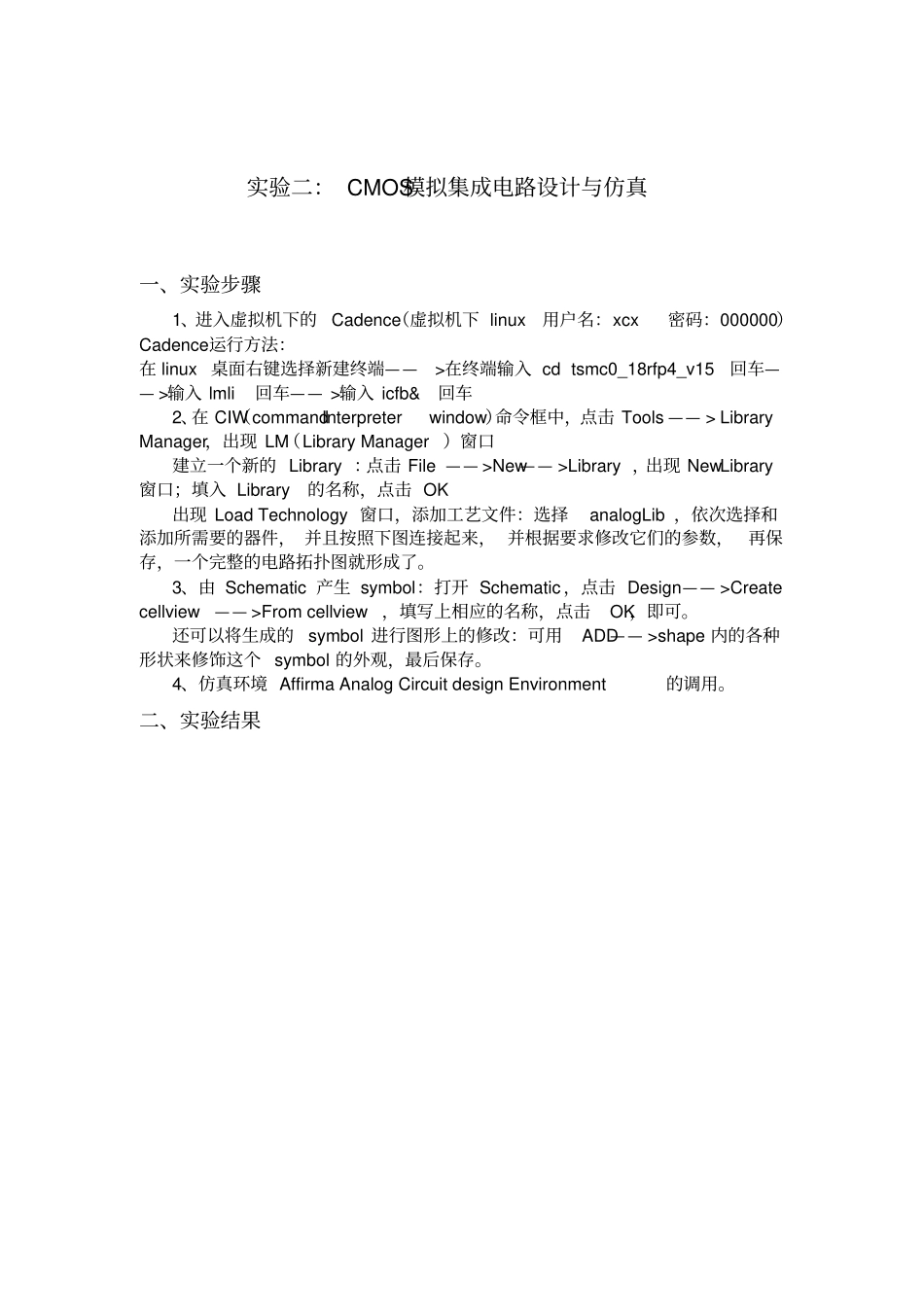

3、由 Schematic 产生 symbol:打开 Schematic ,点击 Design—— >Create cellview—— >From cellview,填写上相应的名称,点击OK,即可

还可以将生成的symbol 进行图形上的修改:可用ADD—— >shape 内的各种形状来修饰这个 symbol 的外观,最后保存

4、仿真环境 Affirma Analog Circuit design Environment的调用

二、实验结果图 1:OPA内部电路图图 2:OPA Symbol图1、失调电压 VOS (1)仿真电路的