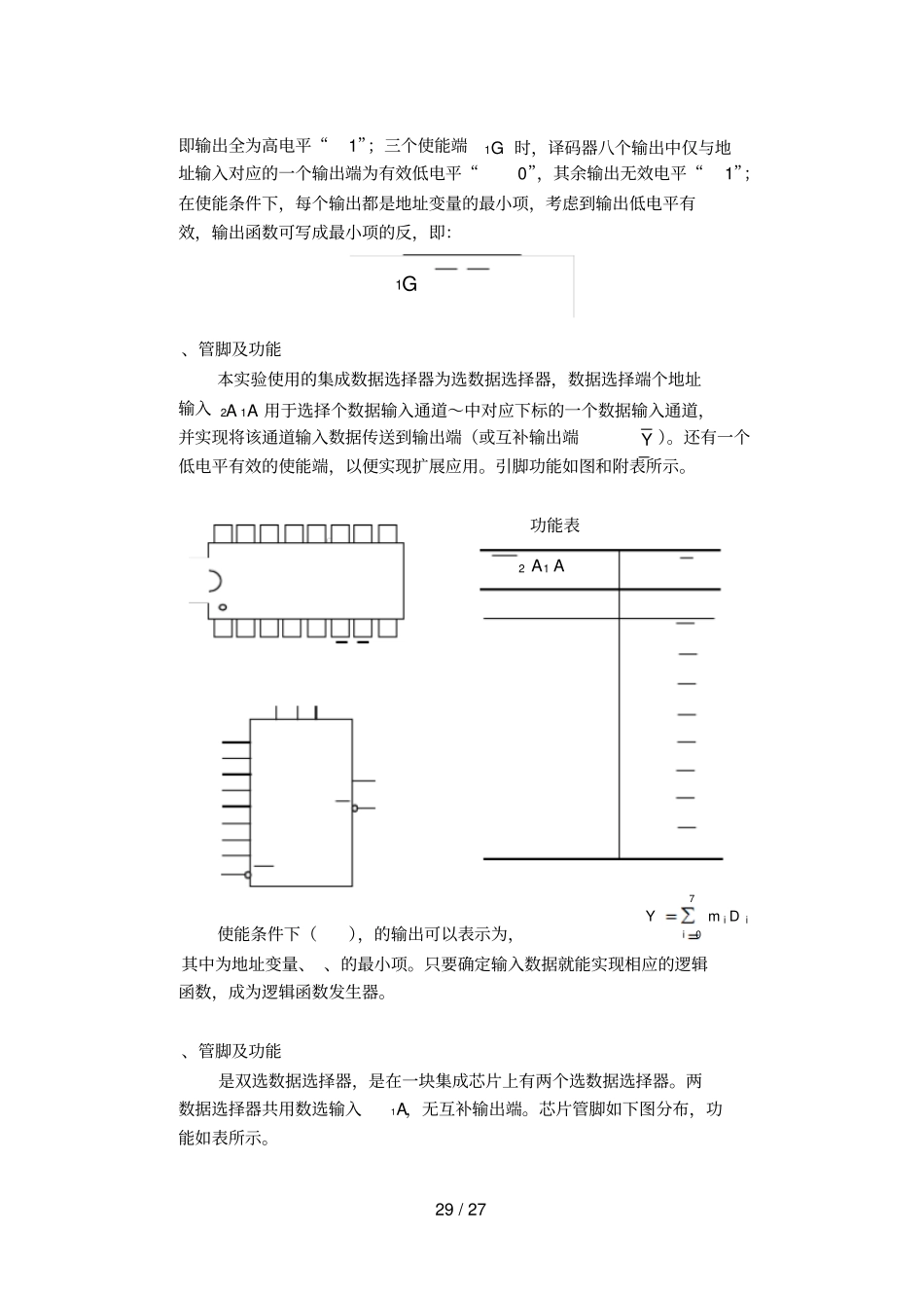

27 / 27 实验六组合逻辑电路设计一、实验目的:、掌握组合逻辑电路的分析与设计方法。、掌握集成门电路的应用。、掌握集成电路译码器与数据选择器的应用。二、预习要求:复习课本中相关内容。、根据题意列出输入、输出真值表。、利用卡诺图化简,写出最简或最合适的逻辑函数表达式。、利用指定门电路实现逻辑功能。、画出已设计完成的逻辑电路及实验用的接线图。三、实验内容:、设计三变量表决电路:要求: 画出逻辑电路图,设计相应表格。 自拟实验方案, 测试电路的逻辑功能是否与设计功能一致。()用与非门实现。()用译码器(、 )实现。()用数据选择器(及)实现。、用异或门和与非门实现全加器电路:要求: 画出逻辑电路图,设计相应表格。 自拟实验方案, 测试电路的逻辑功能是否与设计功能一致。四、实验仪器及元器件数字实验箱、万用表、 、,、、、、等。五、实验报告:画出各部分逻辑电路图、真值表、及列出逻辑表达式,整理实验结果并进行分析,说明组合电路的特点和分析、设计方法。六、实验用门电路介绍:28 / 27 、、及管脚及功能本实验所使用的(双四输入与非门)、(四二输入与非门)和(四输入或门)是一种低功耗肖特基集成门电路,其及引线功能及排列图如下:ABYABCDY、管脚及功能双排直立式集成线线译码器各引脚排列及功能如图所示。由功能表可知:三个使能端1G 时,八个译码输出都是无效电平,1 G2A2 A1 A 译码器真值表1A 2A 3A 4A 1A 1C 2A 2C 2A29 / 27 即输出全为高电平“1”;三个使能端1G 时,译码器八个输出中仅与地址输入对应的一个输出端为有效低电平“0”,其余输出无效电平“1”;在使能条件下,每个输出都是地址变量的最小项,考虑到输出低电平有效,输出函数可写成最小项的反,即:、管脚及功能本实验使用的集成数据选择器为选数据选择器,数据选择端个地址输入 2A 1A 用于选择个数据输入通道~中对应下标的一个数据输入通道,并实现将该通道输入数据传送到输出端(或互补输出端Y )。还有一个低电平有效的使能端,以便实现扩展应用。引脚功能如图和附表所示。使能条件下(),的输出可以表示为,其中为地址变量、 、的最小项。只要确定输入数据就能实现相应的逻辑函数,成为逻辑函数发生器。、管脚及功能是双选数据选择器,是在一块集成芯片上有两个选数据选择器。两数据选择器共用数选输入1A,无互补输出端。芯片管脚如下图分布,功能如表所示。2 A1 A 功能表1G ...