I2C 通信的接口之上拉电阻在一些 PCB 的 layout 中,大家往往会看到在 I2C 通信的接口处,往往会接入一个 4

7K 的电阻,有的 datasheet 上面明确有要求,需要接入,有的则没有要求

I2C 接口对于单片机来讲,有些 IO 内部的上拉电阻可以使能,这样就省去了外部的上拉电阻,这是对于单片机带有标准 I2C 通信协议接口,若是只带有模拟 I2C协议接口,那么就需要考虑接入上拉电阻问题

下图是摄像头进行配置通信时SCL 和 SDA 需要进行上拉电阻的连接

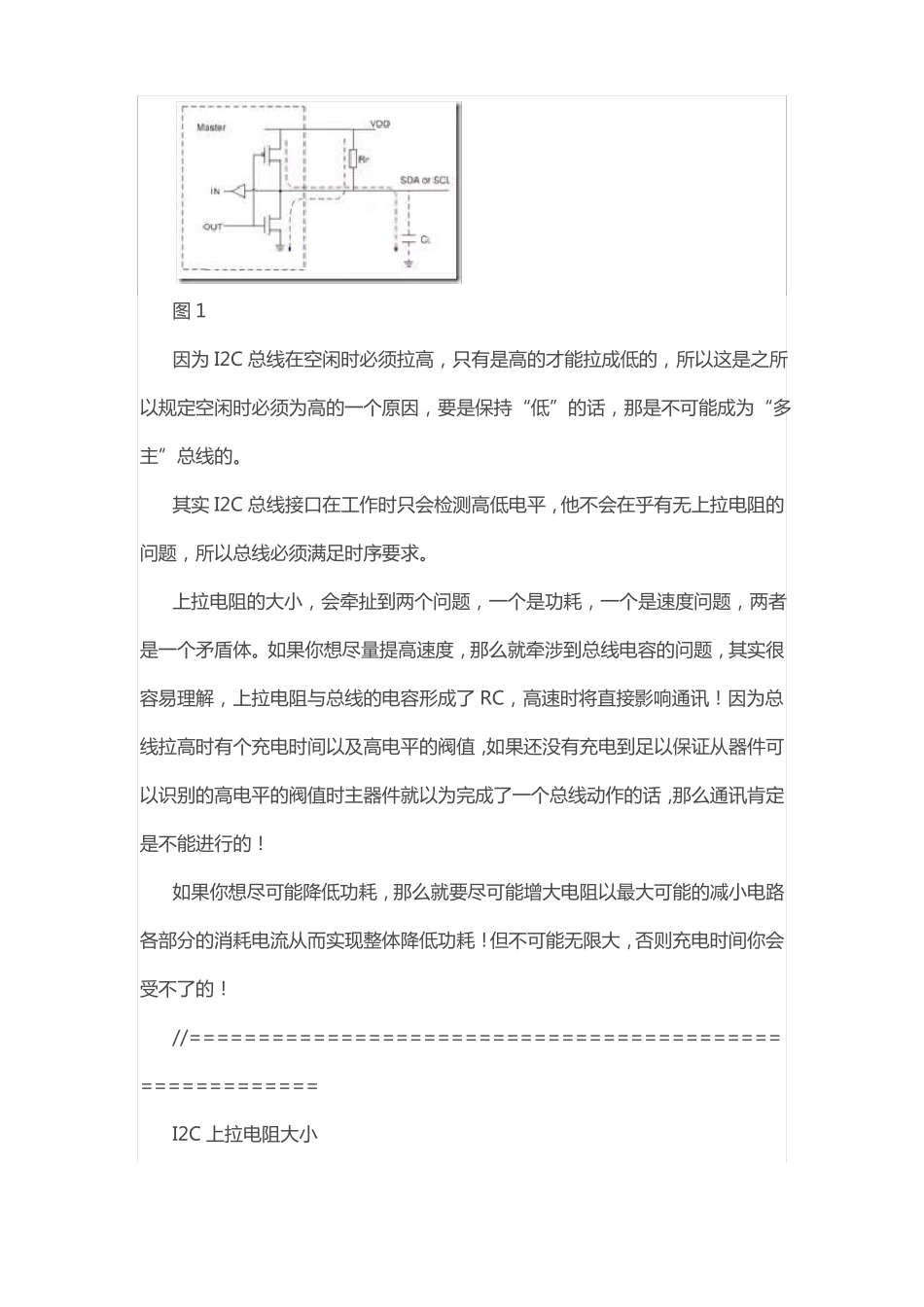

在大多数情况下,由于 I2C 接口采用 Open Drain 机制,器件本身只能输出低电平,无法主动输出高电平,只能通过外部上拉电阻 RP 将信号线拉至高电平

因此 I2C 总线上的上拉电阻是必须的,如图 1 所示

图 1因为 I2C 总线在空闲时必须拉高,只有是高的才能拉成低的,所以这是之所以规定空闲时必须为高的一个原因,要是保持“低”的话,那是不可能成为“多主”总线的

其实 I2C 总线接口在工作时只会检测高低电平,他不会在乎有无上拉电阻的问题,所以总线必须满足时序要求

上拉电阻的大小,会牵扯到两个问题,一个是功耗,一个是速度问题,两者是一个矛盾体

如果你想尽量提高速度,那么就牵涉到总线电容的问题,其实很容易理解,上拉电阻与总线的电容形成了 RC,高速时将直接影响通讯

因为总线拉高时有个充电时间以及高电平的阀值,如果还没有充电到足以保证从器件可以识别的高电平的阀值时主器件就以为完成了一个总线动作的话,那么通讯肯定是不能进行的

如果你想尽可能降低功耗,那么就要尽可能增大电阻以最大可能的减小电路各部分的消耗电流从而实现整体降低功耗

但不可能无限大,否则充电时间你会受不了的

//========================================================I2C 上拉电阻