单时钟同步2 4 进制计数器课程设计报告 1 1

设计任务 1

1 设计目的 1

了解计数器的组成及工作原理

进一步掌握计数器的设计方法和计数器相互级联的方法

进一步掌握各芯片的逻辑功能及使用方法

进一步掌握数字系统的制作和布线方法

熟悉集成电路的引脚安排

2 设计指标 1

以24 为一个周期,且具有自动清零功能

能显示当前计数状态

3 设计要求 1

画出总体设计框图,以说明计数器由哪些相对独立的功能模块组成,标出各个模块之间互相联系,时钟信号传输路径、方向

并以文字对原理作辅助说明

设计各个功能模块的电路图,加上原理说明

选择合适的元器件,利用multisim 仿真软件验证、调试各个功能模块的电路,在接线验证时设计、选择合适的输入信号和输出方式,在确定电路充分正确性同时,输入信号和输出方式要便于电路的测试和故障排除

在验证各个功能模块基础上,对整个电路的元器件和布线进行合理布局

打印PCB 板,腐蚀,钻孔,插元器件,焊接再就对整个计数器电路进行调试

设计思路与总体框图

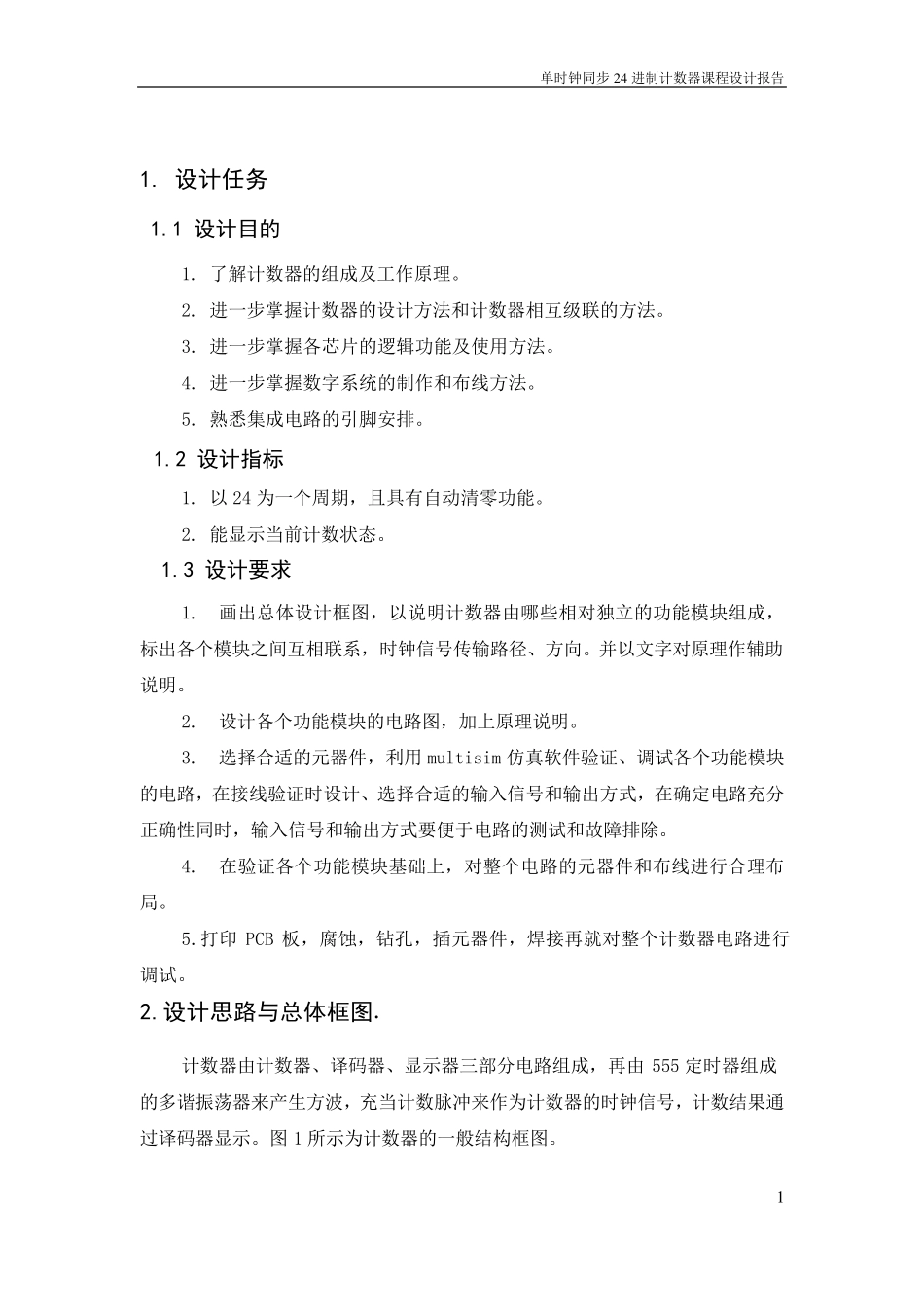

计数器由计数器、译码器、显示器三部 分电路组成,再由555 定时器组成的多 谐 振 荡 器来 产 生 方波 ,充当计数脉 冲 来 作为计数器的时钟信号,计数结 果 通过 译码器显示

图1 所 示为计数器的一般 结 构 框图

单时钟同步2 4 进制计数器课程设计报告 2 CR CR CR ▲ 图 1 计数器结 构 框 图 3

系统硬件电路的设计 3

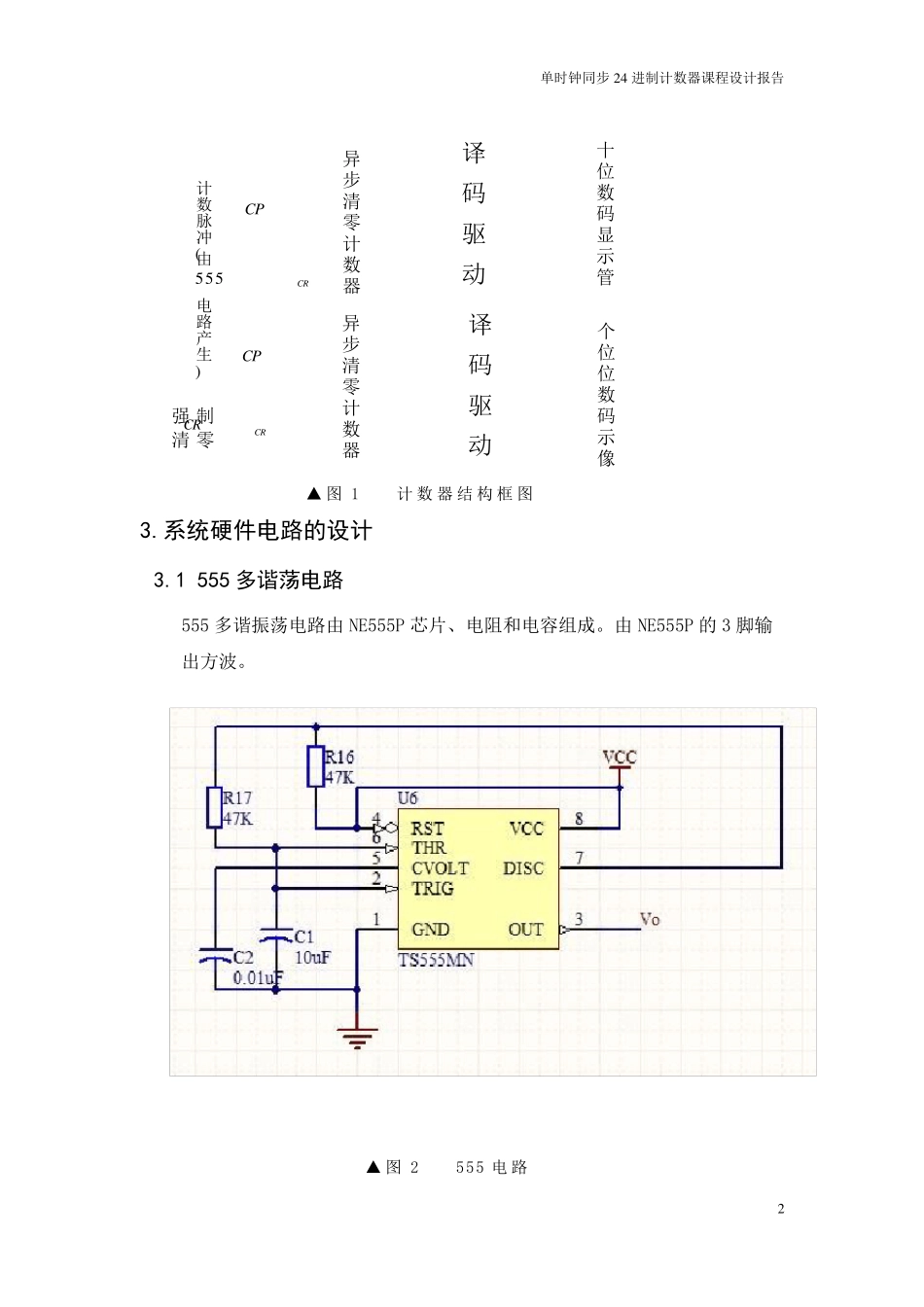

1 555 多谐荡电路 555 多谐振荡电路由 NE555P 芯片、电阻和电容组成

由 NE555P 的 3 脚输 出方波

▲ 图 2 555 电 路 计数脉冲(由5 5 5电路产生) 异步清零计数器 十位数码显示管 译码驱动 异步清零计数器 个位位数码示像译码驱