Cadence Allegro 16

5 层叠设置 ——孙海峰 对于刚学习 Cadence Allegro ,或者刚从其他 EDA 软件(如 Protel)转为Allegro 使用上的朋友,其颜色设置、层叠意义往往使人望而却步

如此多的额叠层,更细致的、更可靠的层叠设置,如何更好的理解和把握,哪些层叠对于我们设计是常用或必需的呢,我将在以下做详细的介绍

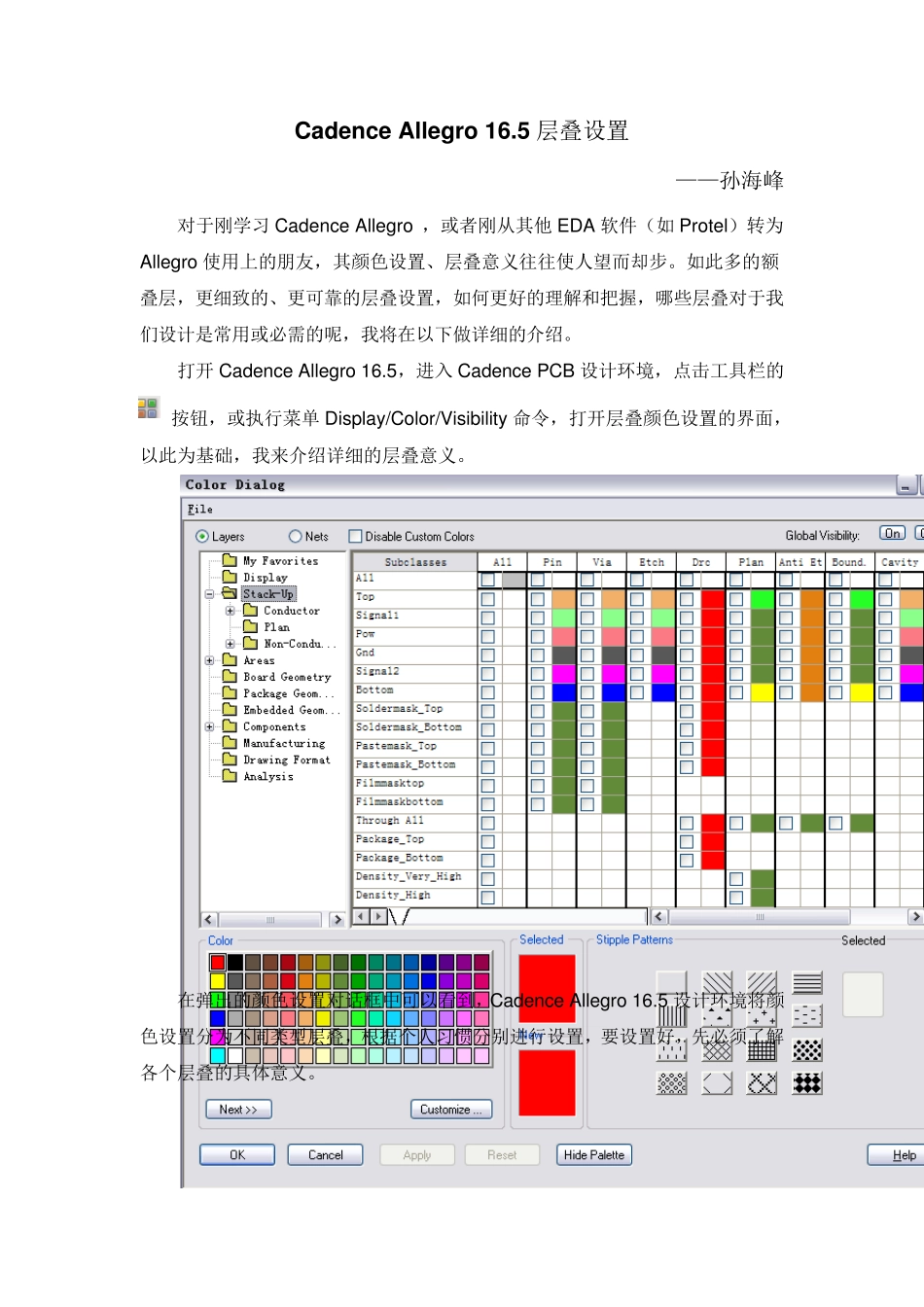

打开 Cadence Allegro 16

5,进入 Cadence PCB 设计环境,点击工具栏的按钮,或执行菜单 Display /Color/Visibility 命令,打开层叠颜色设置的界面,以此为基础,我来介绍详细的层叠意义

在弹出的颜色设置对话框中可以看到,Cadence Allegro 16

5 设计环境将颜色设置分为不同类型层叠,根据个人习惯分别进行设置,要设置好,先必须了解各个层叠的具体意义

1、 PCB 基本叠层 Stack-u p 设置 a) Subclass 子层叠,表示 PCB 中具体层叠,包括:Top 层、Bottom 层、内层(POW/GND)、阻焊层(Soldermask_Top/Soldermask_Bottom )、加焊层(Pastemak_Top/Pastemask_Bottom ),其他 Subclass 子层叠目前设计中不需要用到,包括底片应用层(Filmmasktop/Filmmaskbottom)等,这些不常用的层叠不用花时间去了解的,与目前无关

b) 子层叠相应的对象 Objects,与上述的 Subclass 一起使用,用以显示不同子层叠上相应对象,包括子层叠上对应的 Pin 引脚、Via 过孔、Etch 走线、DRC 规则错误、Plan 覆铜平面、Anti Etch 隔离走线(用于铜皮分割),这样既可配合子层叠,设置对应层不同对象的颜色

此外, Boundary 轮