SPI 接口的FLASH ROM AT45DB161D 的驱动方法 ( 1)芯片介绍 AT45DB161D 是串行接口的闪存芯片,可工作在2

7V, 可广泛应用于数据语音、图像、程序代码数据存储中

AT45DB161D 支持RapidS 串行接口,适用于高速场合

RapidS串行接口是与SPI 相兼容的,速度可达到66MHz

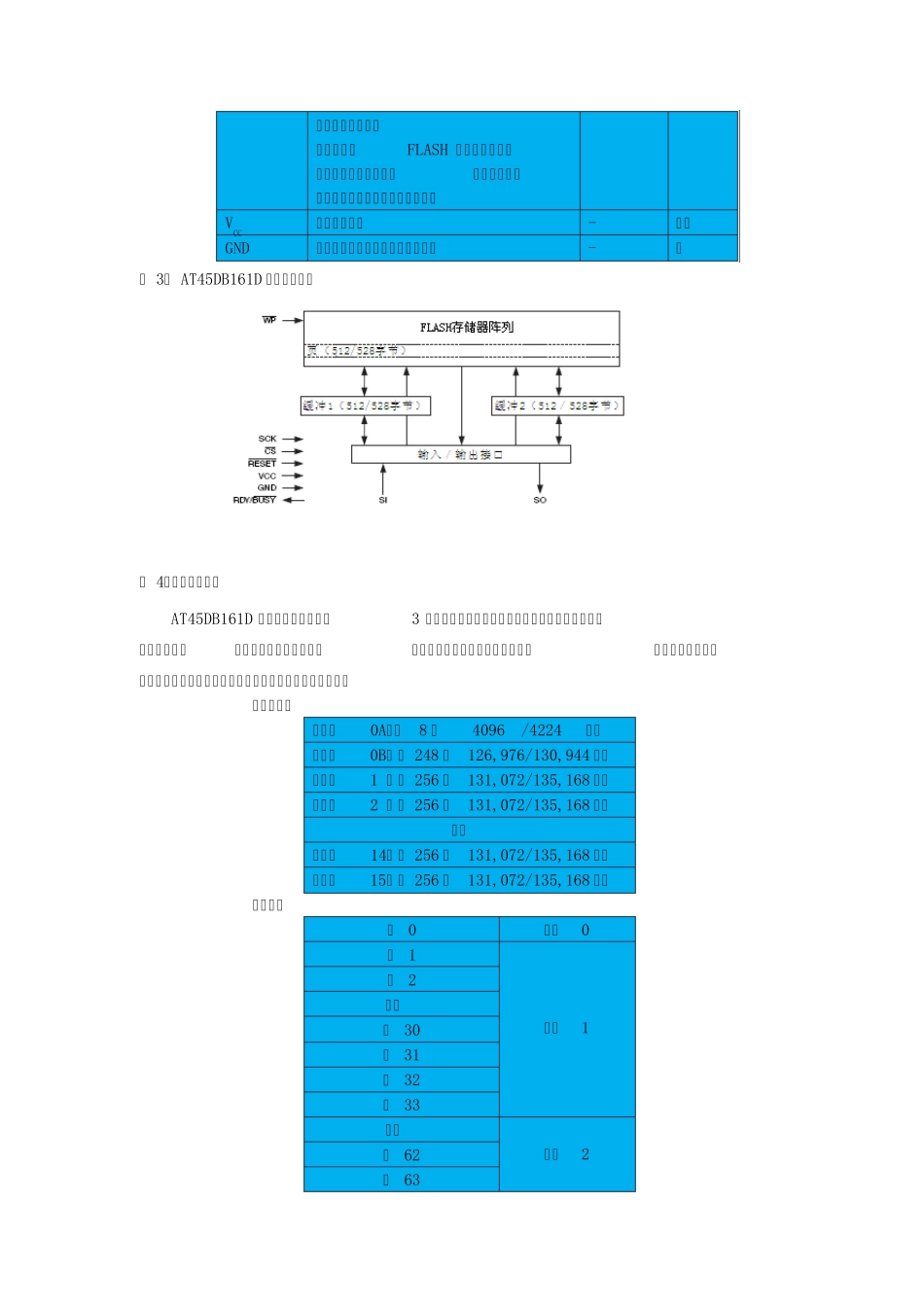

它包含有17,301,504 个位,被组织为4096个页,每个页512 或 528 个字节

除了主存储器,AT45DB161D 还包括两个SRAM 数据缓冲区,每个缓冲区512/528 个字节

在主存储器正在编程时,缓冲区是允许接收数据的,并且支持数据流式写入

与并行FLASH 储存器不同,它采用RapidS 串行接口,从而大大减少了可用引脚数量,同时也提高了系统可靠性,降低了开关噪声,缩小了封装体积

可以应用于商业、工业等需要高密度、低引脚数、低电压与低功耗的应用场合

AT45DB161D 允许简单的在系统重新编程,而无需输入高编程电压

芯片可以采用2

6V 或 2

6V 单电源供电,进行编程与读取操作

它可以通过#CS 来进行使能,并通过三线接口(SI、 SO、 SCK)进行数据通信

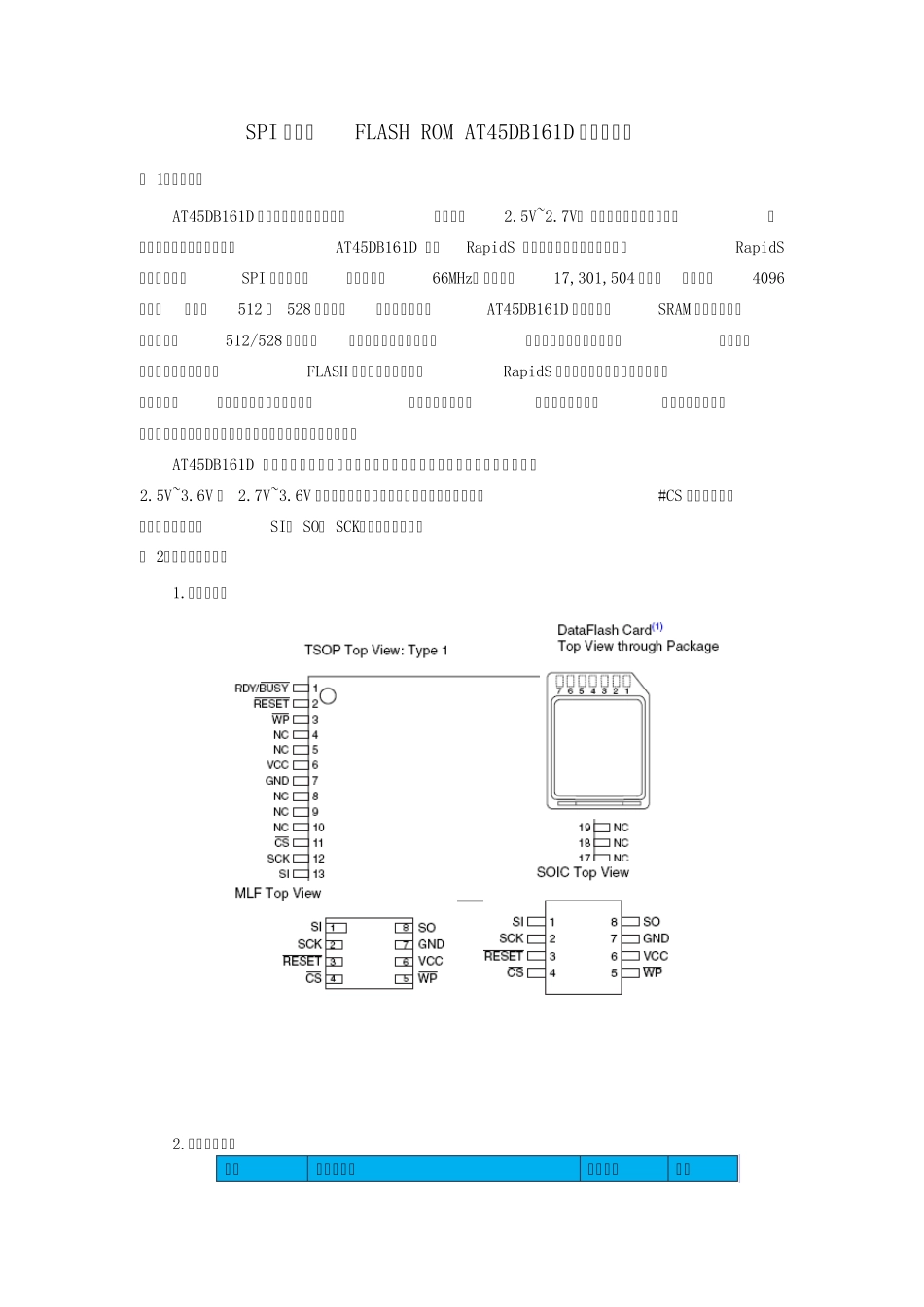

( 2)引脚配置与封装 1

芯片封装图 2

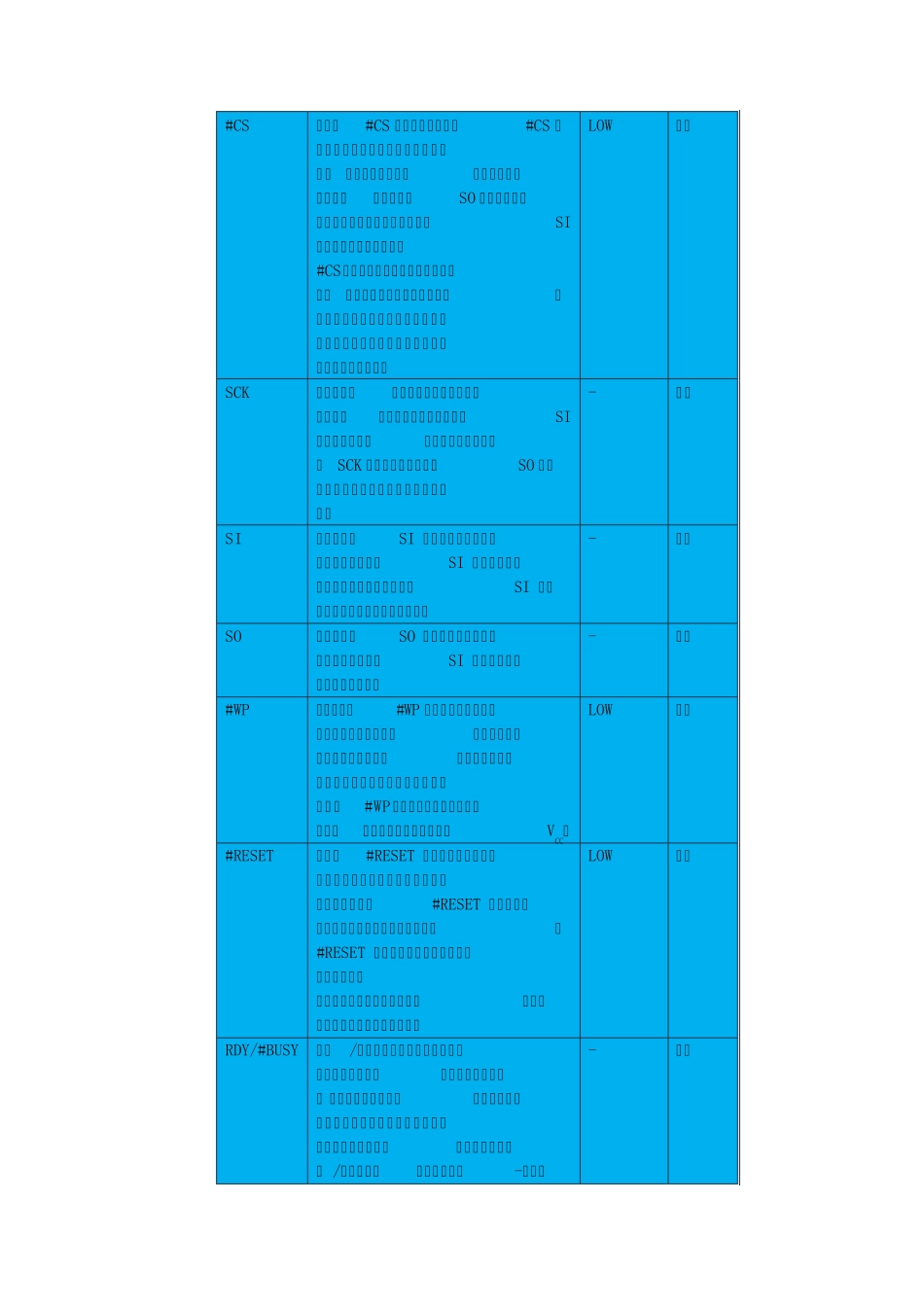

引脚功能详述 符号 名称与功能 有效电平 类型 #CS 片选:#CS 用以选中芯片

当#CS 被设置为无效状态时,芯片则不被选中, 并且处于闲置状态(不是深度睡眠状态),输出引脚SO 处于高阻态

当芯片未被选中时,从输入引脚SI输入的数据将不被接受

#CS引脚上的下降沿将会启动一个操作,而上跳沿则会结束一个操作

在一个内部操作如芯片内部的编程或擦除周期内,芯片不会进入闲置状态,直到操作完毕

LOW 输入 SCK 串行时钟:此引脚用来向芯片提供时钟信号,有来控制数据流的出入

SI引脚上的