1 单片机教程 (Cortex -M0 处理器) 第1 章 Cortex -M0 的处理器和内核外设 1

1 系统接口 1

2 集成的可配置调试 1

3 Cortex -M0 处理器的特性小结 1

4 Cortex -M0 内核外设 第2 章 Cortex -M0 处理器 2

1 编程模型 2

2 存储模型 2

3 异常模型 2

4 故障处理 2

5 功耗管理 第3 章 外设 3

1 关于ARMCortex -M0 3

2 嵌套向量中断控制器 3

3 系统控制块 3

4 系统定时器,Sy sTick 2 第1 章 Cortex -M0 的处理器和内核外设 Cortex-M0 处理器是一个入门级(entry-level)的32 位ARM Cortex 处理器,设计用在更宽范围的嵌入式应用中

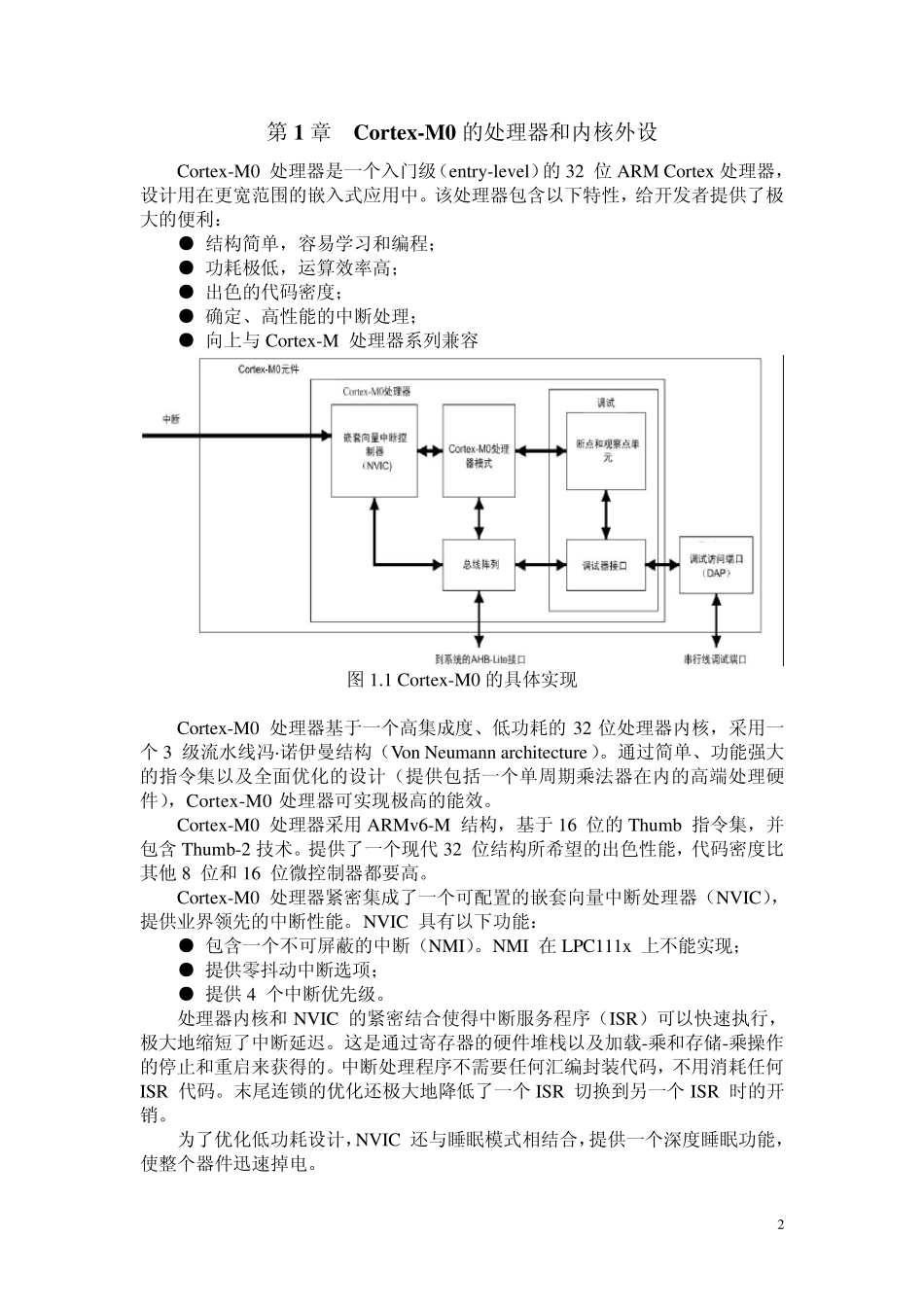

该处理器包含以下特性,给开发者提供了极大的便利: ● 结构简单,容易学习和编程; ● 功耗极低,运算效率高; ● 出色的代码密度; ● 确定、高性能的中断处理; ● 向上与 Cortex-M 处理器系列兼容 图 1

1 Cortex-M0 的具体实现 Cortex-M0 处理器基于一个高集成度、低功耗的32 位处理器内核,采用一个3 级流水线冯·诺伊曼结构(Von Neumann architecture)

通过简单、功能强大的指令集以及全面优化的设计(提供包括一个单周期乘法器在内的高端处理硬件),Cortex-M0 处理器可实现极高的能效

Cortex-M0 处理器采用ARMv6-M 结构,基于 16 位的Thumb 指令集,并包含Thumb-2 技术

提供了一个现代 32 位结构所希望的出色性能,代码密度比其他 8 位和16 位微控制器都要高

Cortex-M0 处理器紧密集成了一个可配置的嵌套向量中断处理器(NVIC),提供业界领先的中断性能

NVIC 具有以下功能: ● 包含一