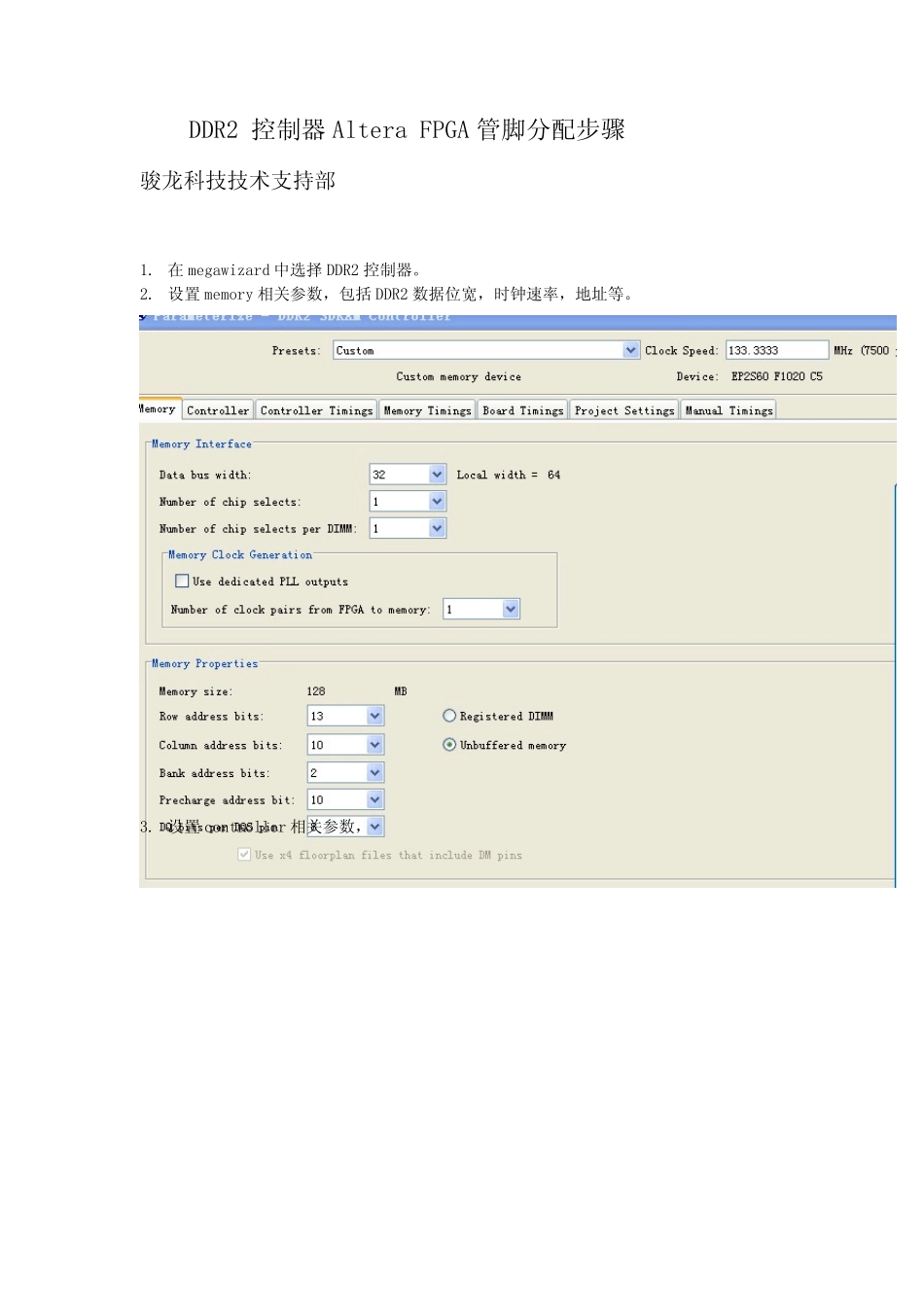

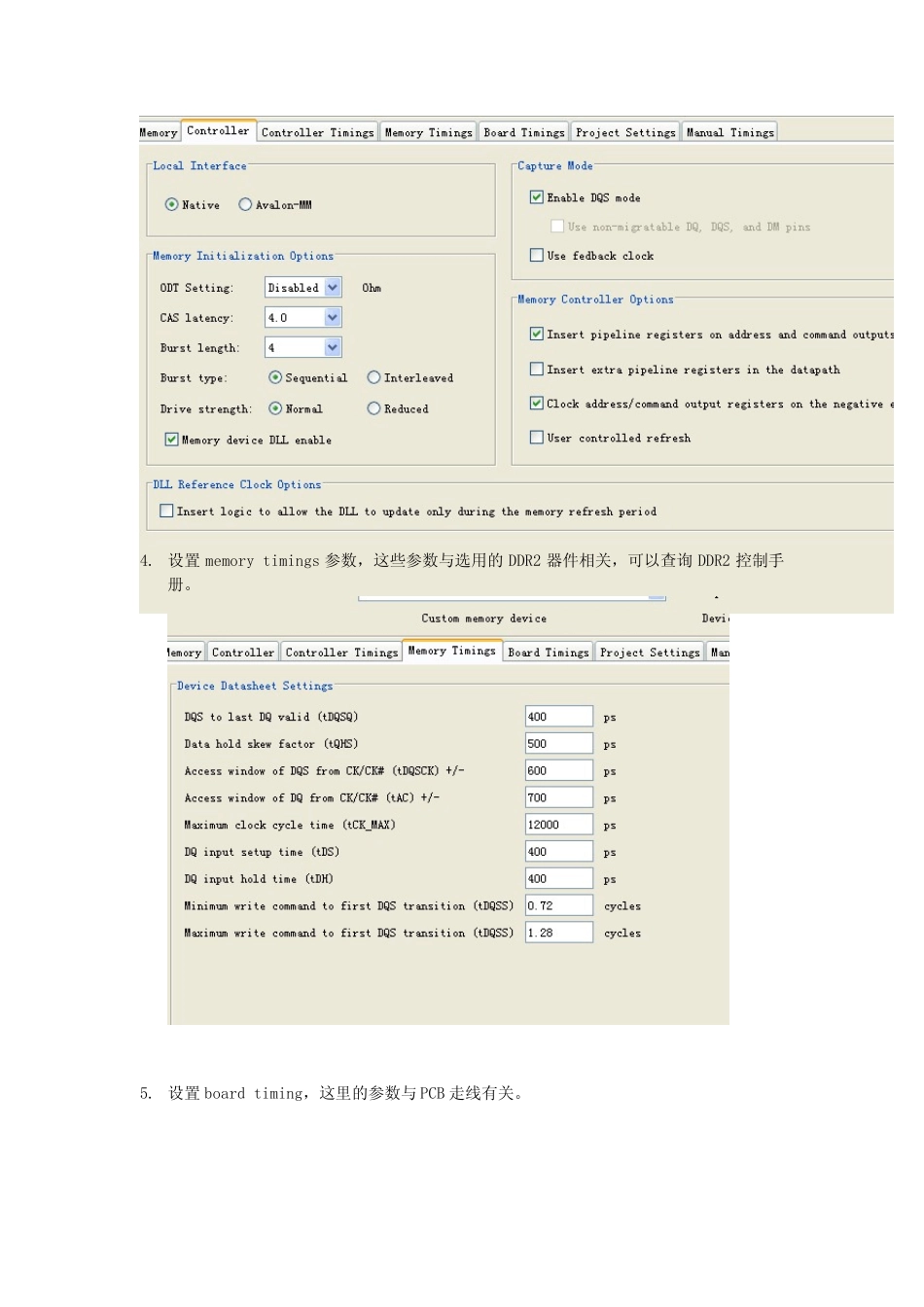

DDR2 控制器Altera FPGA 管脚分配步骤 骏龙科技技术支持部 1. 在megawizard 中选择DDR2 控制器。 2. 设置 memory 相关参数,包括 DDR2 数据位宽,时钟速率,地址等。 3. 设置 controller 相关参数, 4. 设置memory timings 参数,这些参数与选用的DDR2 器件相关,可以查询DDR2 控制手册。 5. 设置board timing,这里的参数与PCB 走线有关。 6. 仿真模型设置,如果需要对生成的IP 进行功能仿真,选上Generate Simulation Model。 7. 生成DDR2 控制器 IP,在工程目录下可以查看到 Altera 提供一个自测程序文件(_example_top.v),把_example_top.v设置为 top level file。 8. 在settings 下的timequest timing analyzer 处添加DDR2 的时序约束文件SDC 文件,如下图。 9. 综合工程和管脚约束:综合完成后运行 tcl scripts(在tools 菜单下):选 中_pin_assignments.tcl,然后点击 RUN。 10. 运行打开pin planner :assignments/pin planner 11. 分配dqs信号到想要的DQS管脚上,注意DQS group有X8/X9mode, X4/X5mode,X16/X18mode. 12. 指定DQ,ADDRESS 和命令信号等到相应的IO bank,但DQ 是跟随DQS 的。如图,只需把location 指定到bank 位置,不需指定到某个 IO 号。 13. 位置指定完成后,全编译! 14. 全编译后查看是否有时序不满足,主要看信息栏,是否有报关键警告。 15. 16. 编译完成,时序也满足要求后运行:assignments/back-annotate assignments 将之前指定到IObank 的管脚反标到特定的IO 管脚上。再查看 pin planner 时,你将会发现上图变为下图所示: 17. 在 assignments 下选择 Pin planner,倒出管脚文件,文件名后缀为*.csv. 18.