DDR 时序测试方法 1

参考文献: RS –Springdale-G/P/PE MCH external design specification(EDS) addendum (number:780) 2

测试目的: 在P4D 项目(Springdale-G/PE)中, 主要看System ddr Data 和Strobe 信号的时序质量是否满足规范要求

测试内容和规范 特别说明:时序测试中参考电平的值为0

5*Vcc_DDR,具体值的计算如下表: symbol parameter min Nom Max Unit VCC_DDR DDR i/o supply voltage 2

5*VCC_DDR (参考电平) 1

35 V Table 1 DDR interface AC characteristics at 400 MHZ (springdale G/PE only) System memory clock timings symbol parameter min max unit figure notes Tck SCMDCLK period 5

0 ns Tch SCMDCLK high time 2

23 ns Tcl SCMDCLK low time 2

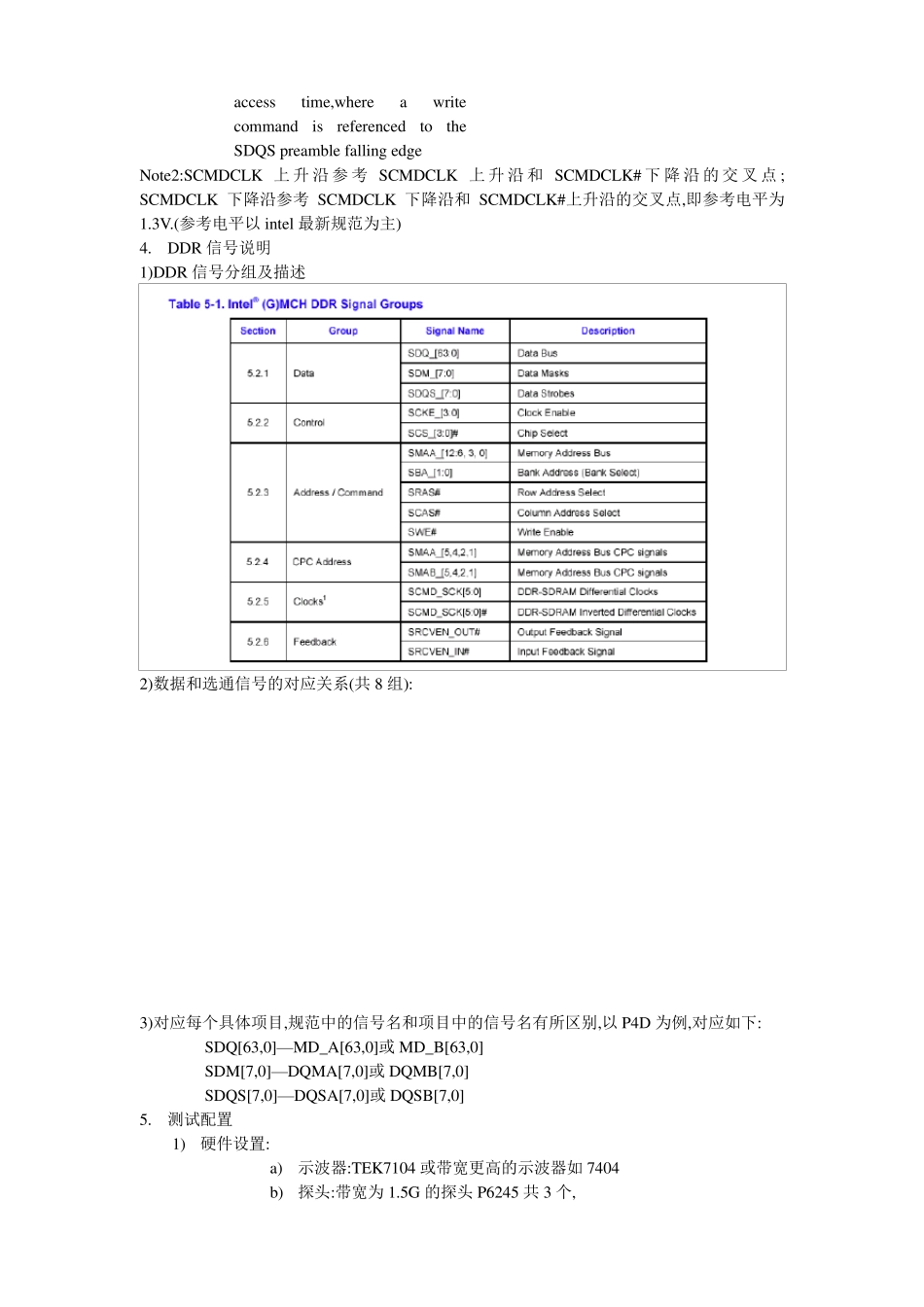

23 ns Tjit SCMDCLK cycle to cycle jitter 300 ps Tskew SCMDCLK /SCMDCLK#) 300 ps system memory data and strobe signal timing symbol parameter min max unit figure notes Tdvb SDQ[63,0],SDM[7:0]valid before SDQ[7:0] rising or falli