基于VHDL的音乐播放器的设计 目前以硬件描述语言(Verilog 或 VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至 FPGA 上进行测试,是现代 IC 设计验证的技术主流

这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式

在大多数的FPGA 里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完整的记忆块

系统设计师可以根据需要通过可编辑的连接把FPGA 内部的逻辑块连接起来,就好像一个电路试验板被放在了一个芯片里

一个出厂后的成品 FPGA 的逻辑块和连接可以按照设计者而改变,所以FPGA 可以完成所需要的逻辑功能

本设计是一种采用FPGA 芯片进行音乐播放,主要由分频器、乐谱存储模块和音乐选择模块组成,利用FPGA 的可编程性,简洁又多变的设计方法,缩短了研发周期

主要采用了 FPGA 芯片,使用VHDL 语言进行编程,使其具有了更强的移植性,更加利于产品的升级

一、设计任务与要求 (1) 能够播放音乐并进行切换选择 用VHDL 语言设计乐音的节拍与音符产生电路;用VHDL 语言设计可控分频器电路;用存储模块 ROM 来存放乐曲,最后能够采用FPGA 芯片进行音乐播放,并通过手动拨换开关来切换不同音乐

(2)能够显示播音音乐的次序 用VHDL 语言进行译码转换,最后在实验板上用数码管显示数字,以此来确定正在播放音乐的顺序,即当播放第一首音乐时,数码管显示数字 1,依次类推

二、设计原理 产生音乐的两个因素是音乐频率和音乐的持续时间,以纯硬件完成演奏电路比利用微处理器(CPU)来实现乐曲演奏要复杂的多,如果不借助于功能强大的EDA 工具和硬件描述语言,凭借传统的数字逻辑技术,即使最简单的演奏电路也难以实现

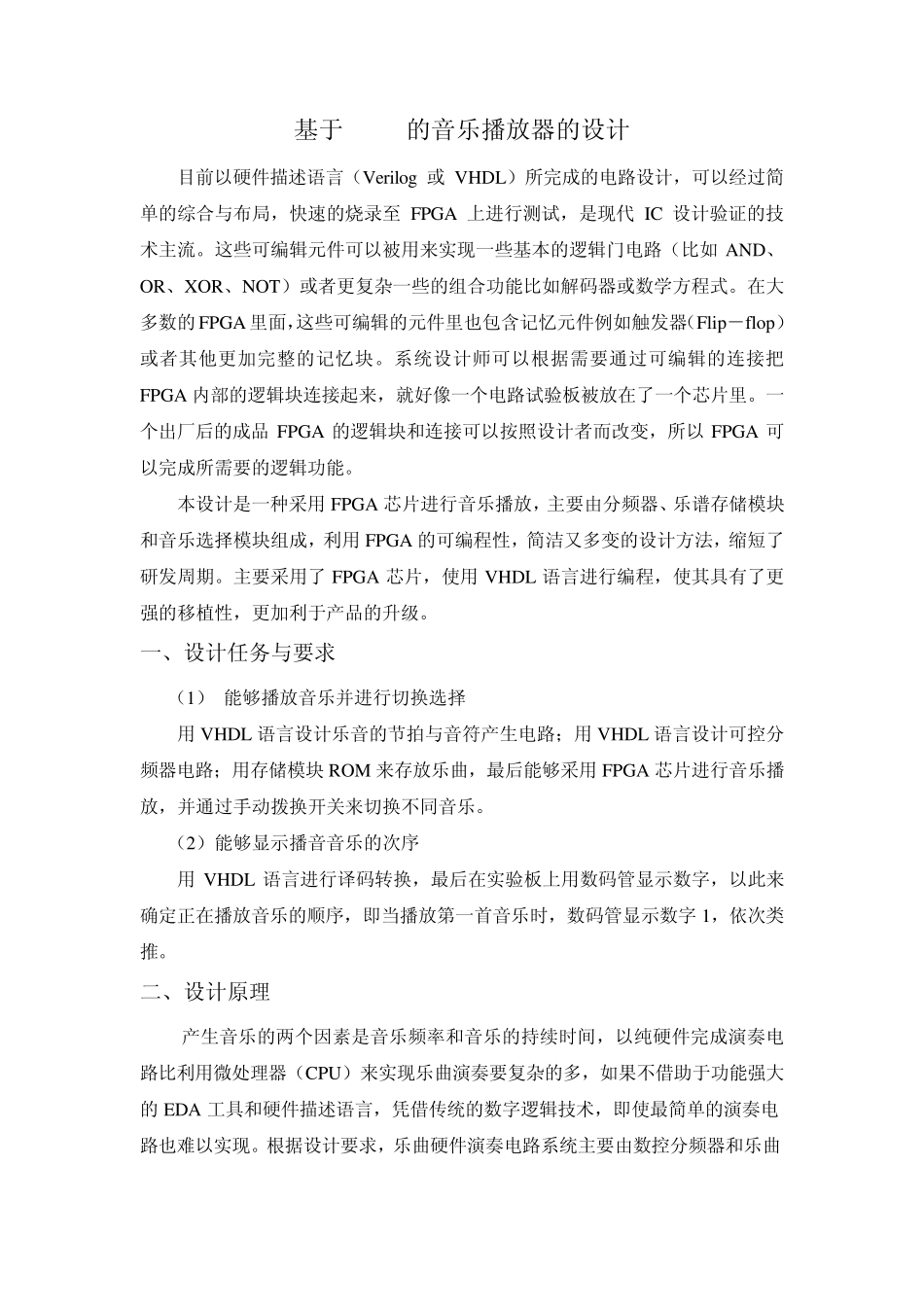

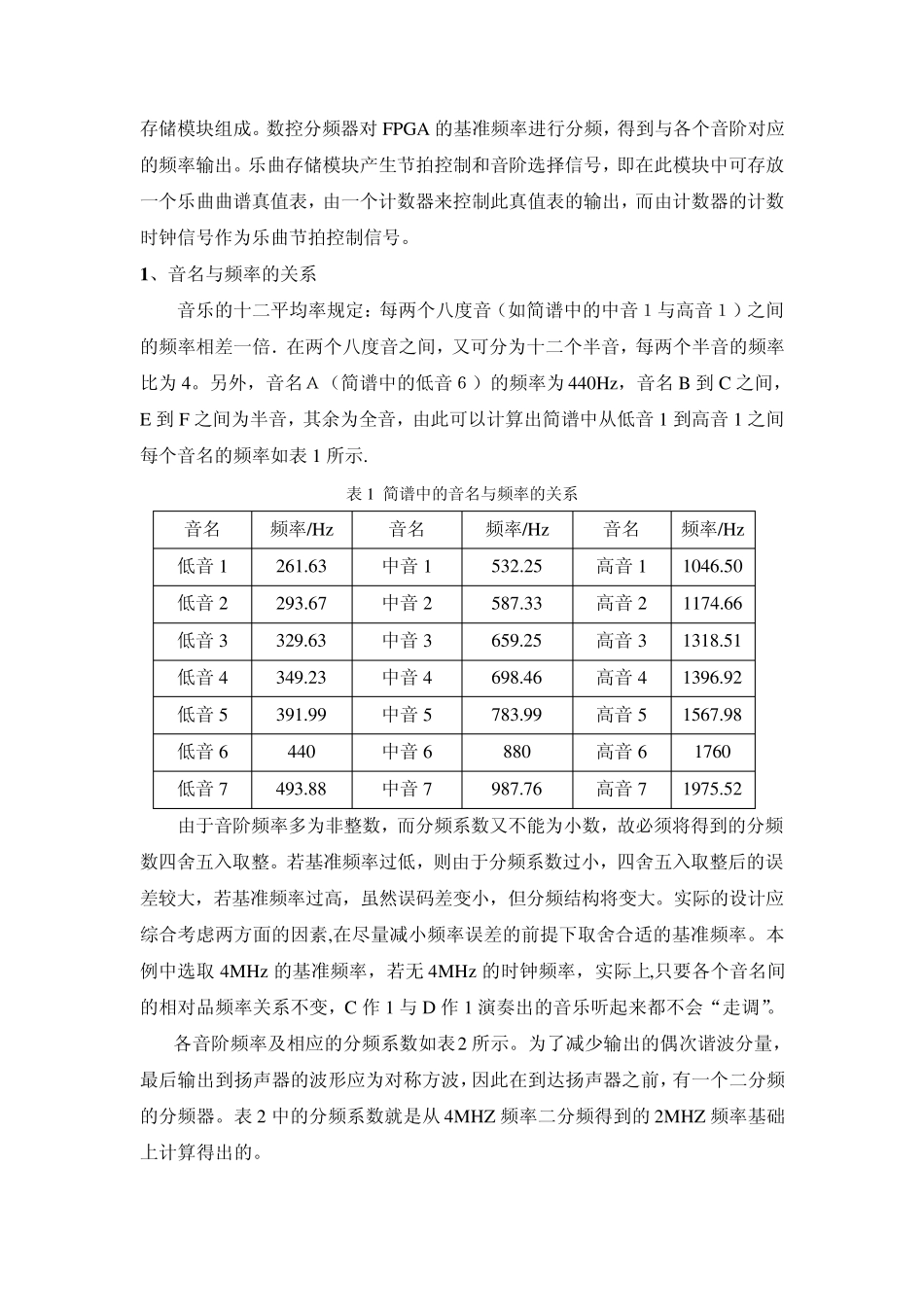

根据设计要求,乐曲硬件演