This is the first of a multi-part series, to introduce FinFET technology to SemiWiki readers

These articles will highlight the technology's key characteristics, and describe some of the advantages, disadvantages, and challenges associated with this transition

Topics in this series will include FinFET fabrication, modeling, and the resulting impact upon existing EDA tools and flows

(And, of course, feedback from SemiWiki readers will certainly help influence subsequent topics, as well

) Scaling of planar FET's has continued to provide performance, power, and circuit density improvements, up to the 22/20nm process node

Although active research on FinFET devices has been ongoing for more than a decade, their use by a production fab has only recently gained adoption

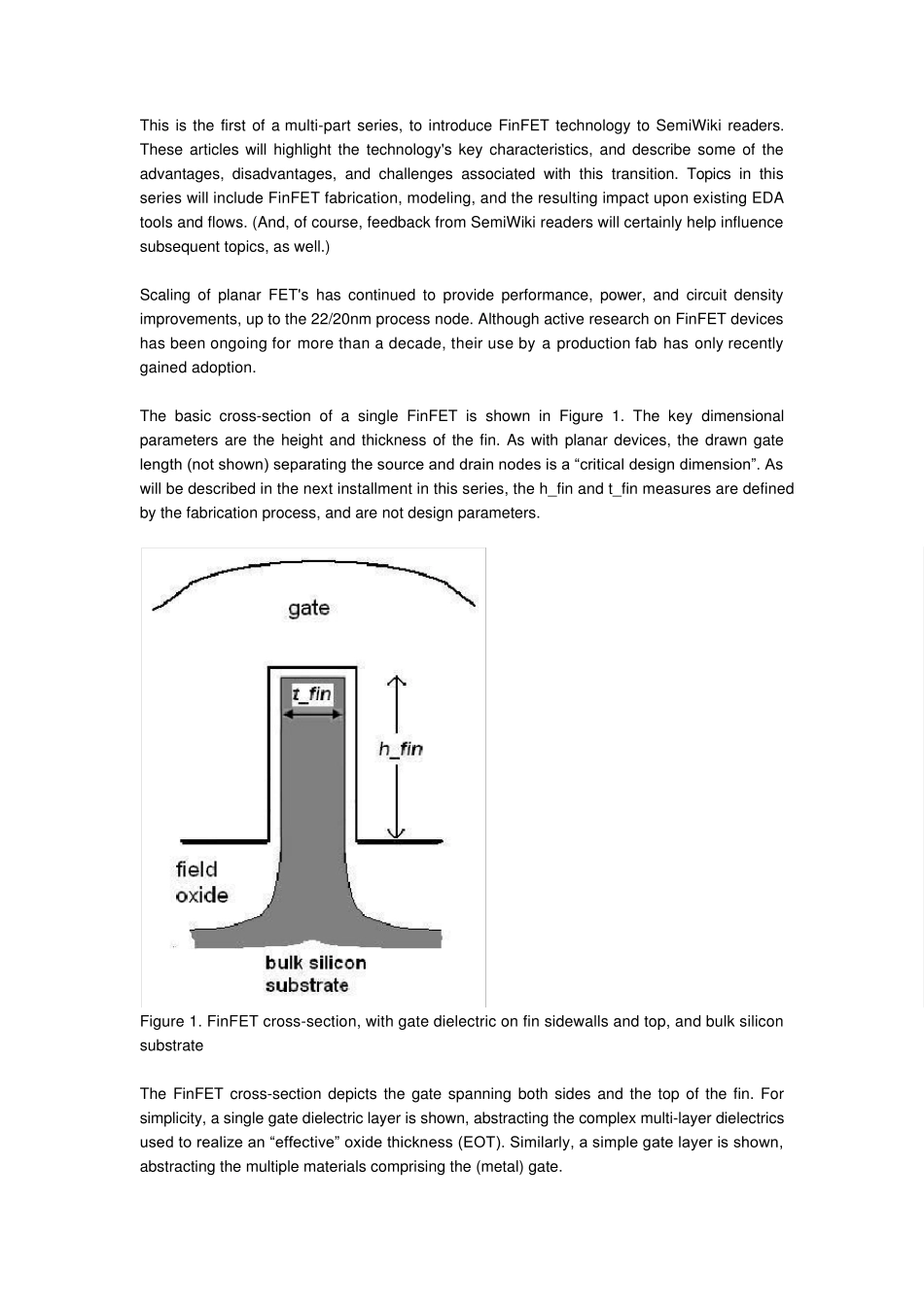

The basic cr