PID 算 法 及 其 FPGA 实 现 PID 控 制 器 结 构 清 晰 , 参 数 可 调 , 适 用 于 各 种 控 制 对 象 , PID 控 制 器 的 核 心 思 想是 针 对 控 制 对 象 的 控 制 需 求 , 建 立 描 述 对 象 动 态 特 性 的 数 学 模 型 , 通 过 PID 参数 整 定 实 现 在 比 例 , 微 分 , 积 分 三 个 方 面 参 数 调 整 的 控 制 策 略 来 达 到 最 佳 系 统 响应 和 控 制 效 果 , 式 子 如 下 : 在 数 字 控 制 系 统 中 , PID 控 制 规 律 的 实 现 必 须 用 数 值 逼 近 的 方 法

当 采 样 周 期 相当 时 , 用 求 和 代 替 积 分 、用 后向差分 代 替 微 分 , 使模 拟 PID 离散化变为差分 方 程

8 就是 我们的 位置式 PID 算 法 : 下 面 就是 我们要实 现 上式 PID 算 法

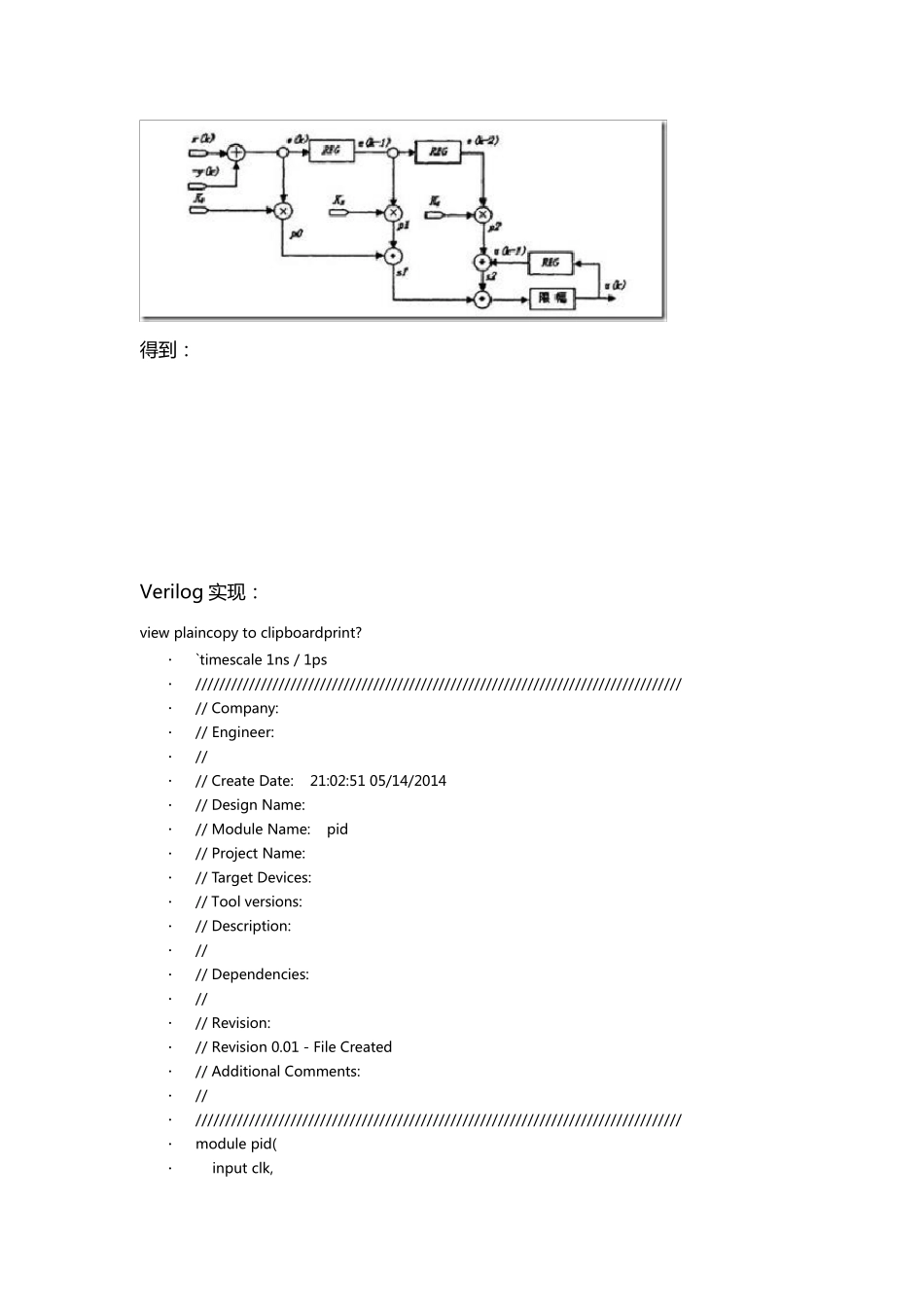

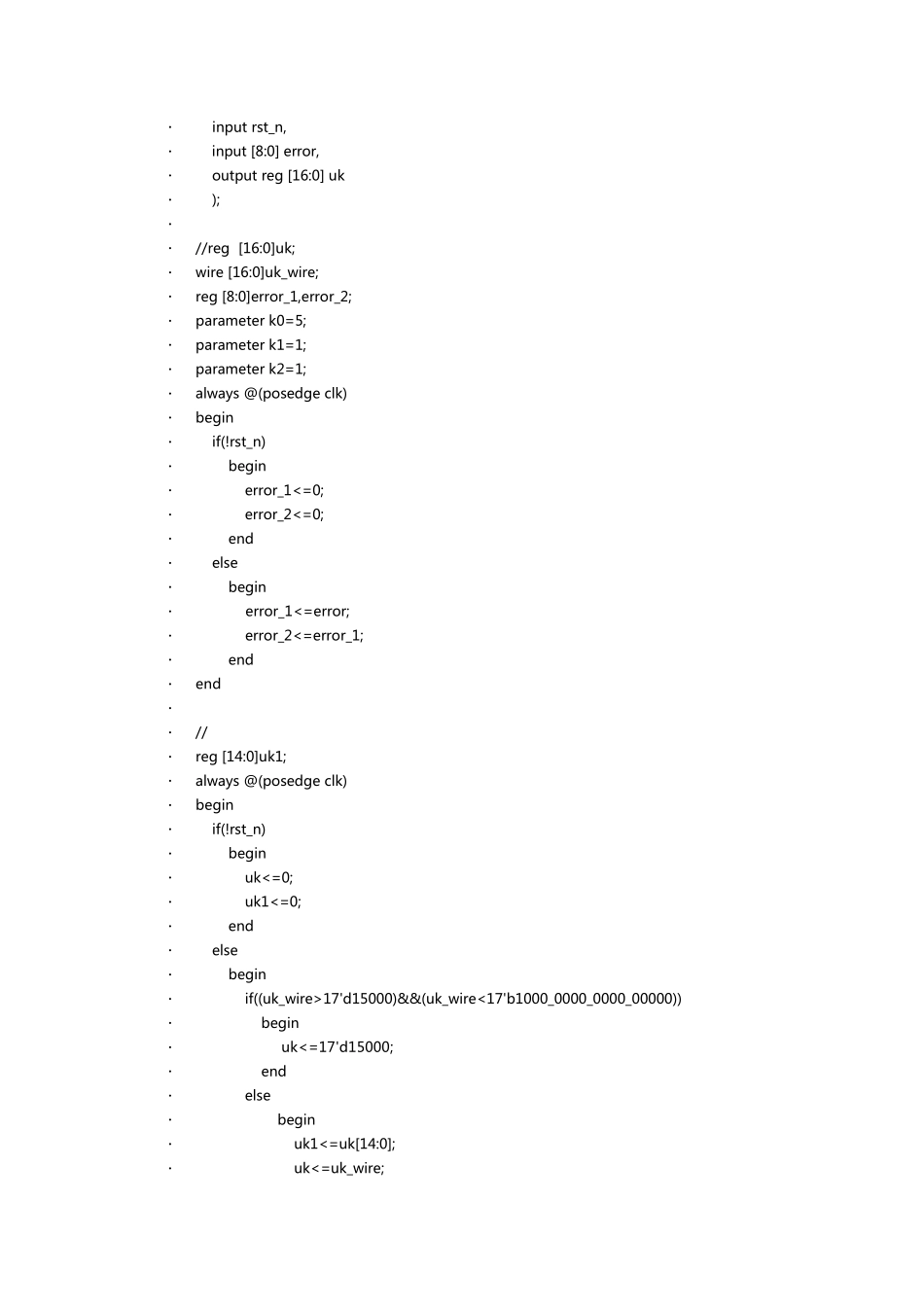

PID 的 FPGA 实 现 : 得 到: Verilog 实现: view plaincopy to clipboardprint

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

// Create Date: 21:02:51 05/14/2014

// Design Name:

// Module Name: pid

// Project Name:

// Target Devices:

// Tool versions:

// Description: