Xilinx FPGA 仿真流程 版本:1

0 (本流程是基于设计代码已完成) 电路设计的各个阶段都与仿真紧密联系在一起的,可以分为以下几个阶段的仿真: 1. 行为级:用于验证电路框架及算法的正确性; 2. RTL 级(寄存器传输级):可以验证功能正确性,一般称为前仿真; 3. 门级:综合出门级网表之后,网表中加入了门的延时信息,仿真结果更接近于真实情况; 4. 后仿真:布局布线后,可以将连线延时加入到网表中,此时可以验证电路的时序是否正确; 实际上我们在编写设计代码时,一般从是RTL 级开始

RTL 级仿真通过,然后直接进入后仿真

只要后仿真通过了,我们就认为设计代码通过验证,可以下载到FPGA 里

所以我们需要仿真的只有 RTL 级和后仿真就行了

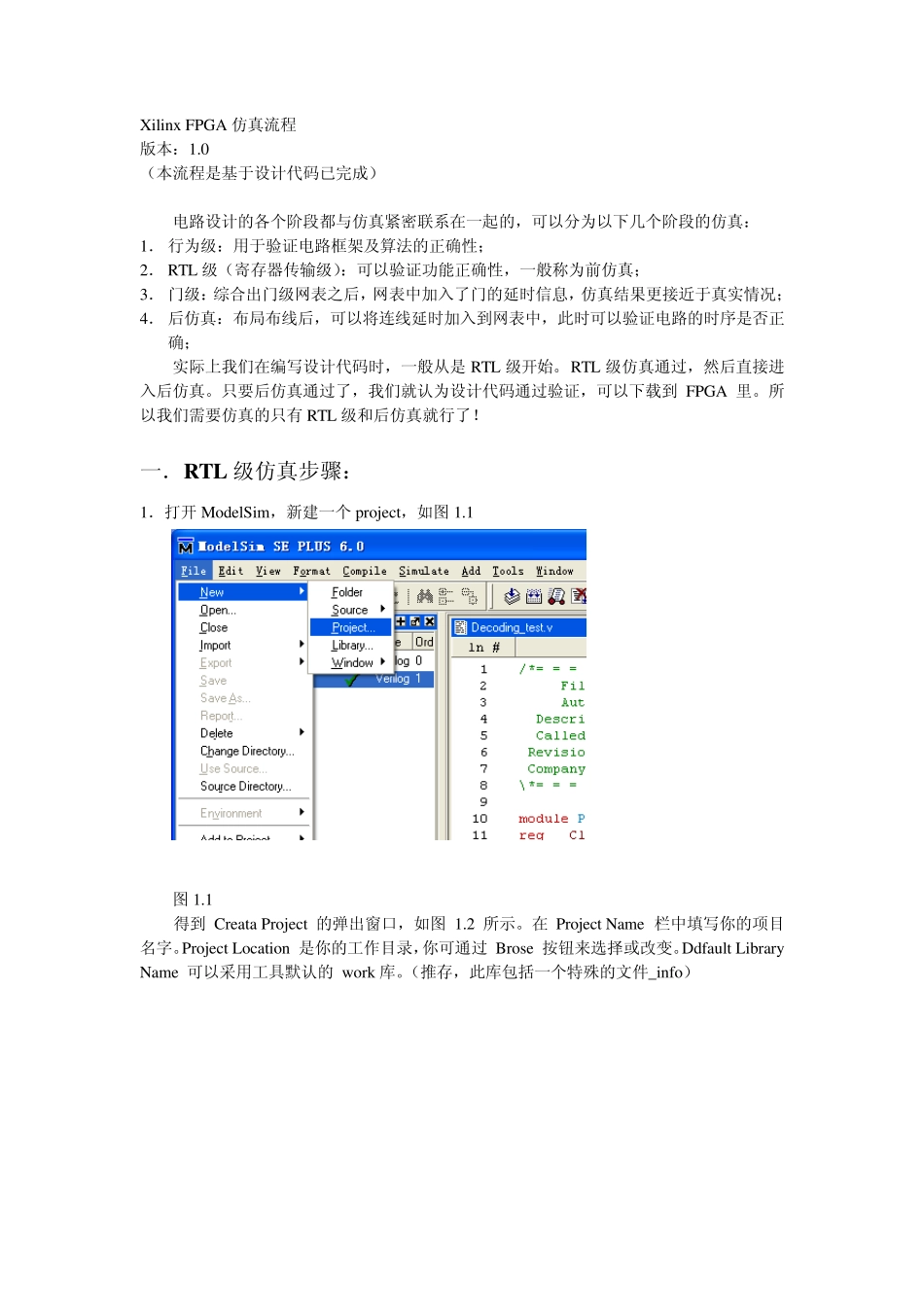

一.RTL 级仿真步骤: 1.打开ModelSim,新建一个project,如图 1

1 得到 Creata Project 的弹出窗口,如图 1

在 Project Name 栏中填写你的项目名字

Project Location 是你的工作目录,你可通过 Brose 按钮来选择或改变

Ddfault Library Name 可以采用工具默认的 work 库

(推存,此库包括一个特殊的文件_info) 图1

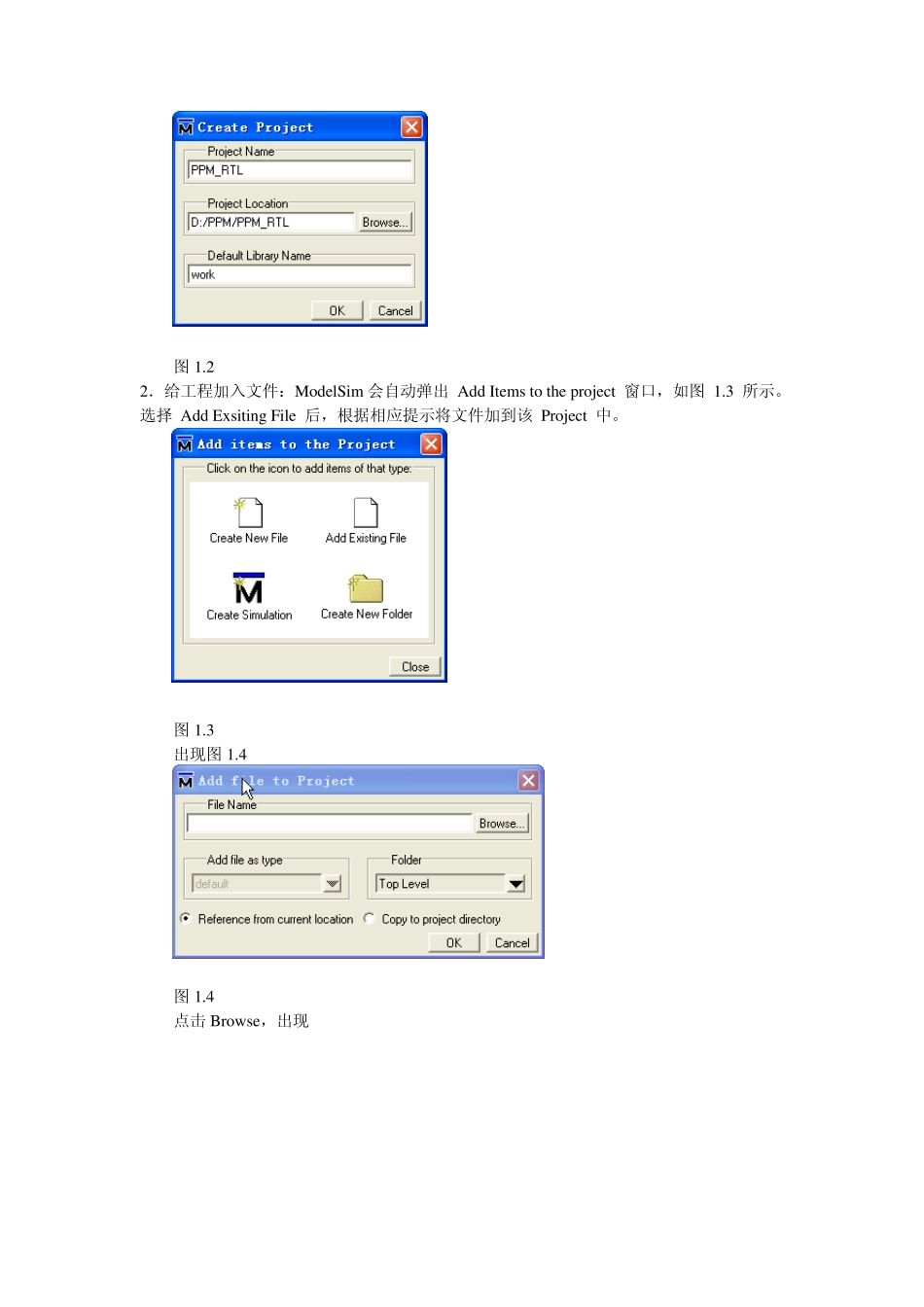

2 2.给工程加入文件:ModelSim 会自动弹出 Add Items to the project 窗口,如图 1

选择 Add Exsiting File 后,根据相应提示将文件加到该 Project 中

3 出现图1

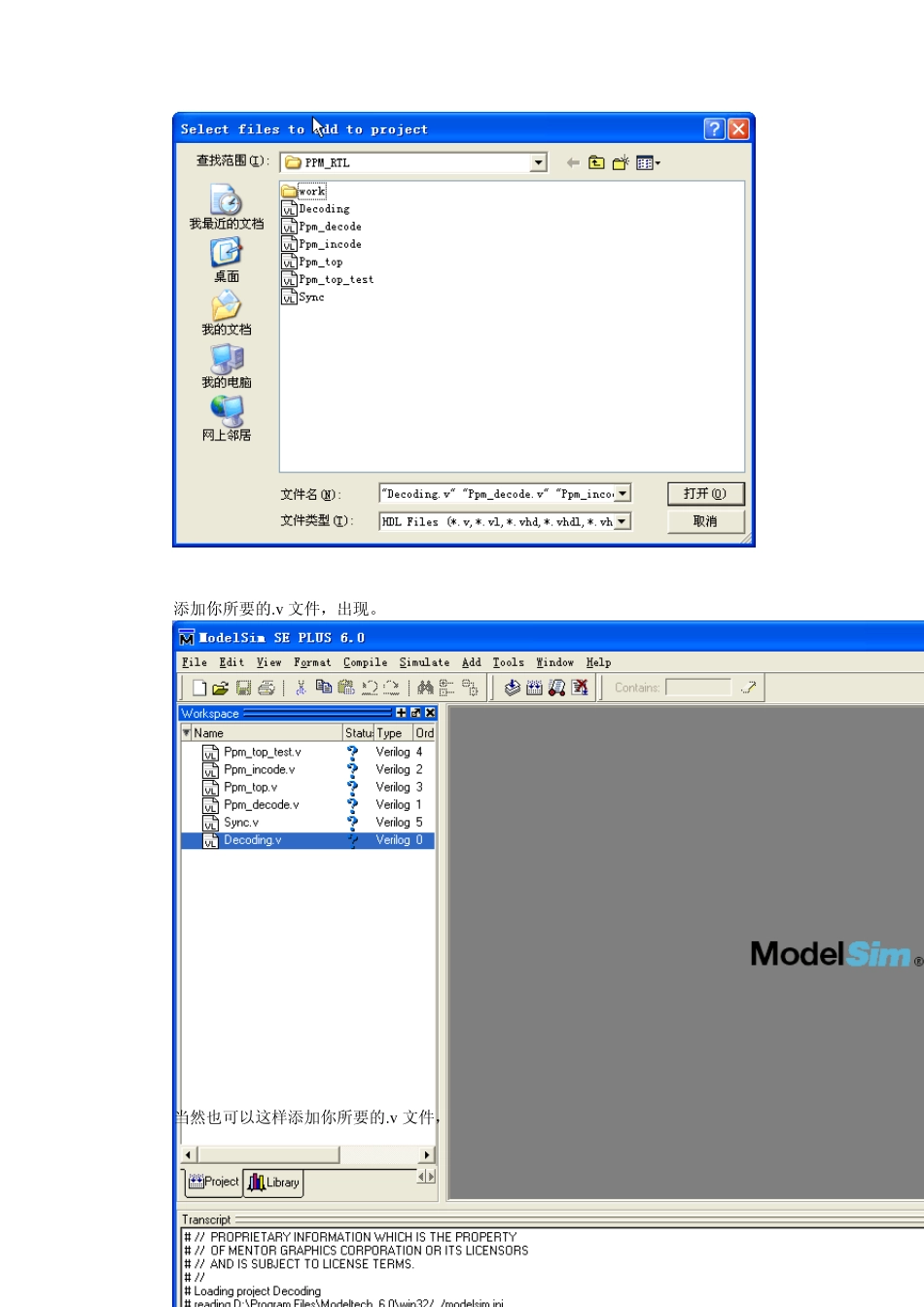

4 点击 Browse,出现 添加你所要的

v 文件,出现

当然也可以这样添加你所要的

v 文件, 3.编译:编译(包括源代码和库文件的编译)

编译可点击 ComlileComlile All 来完成

也可以这样编译文件 编译成功后,所有的文