1 实验一 通用阵列逻辑GAL实现基本门电路的设计 一、实验目的 1

了解GAL22V10 的结构及其应用; 2

掌握GAL 器件的设计原则和一般格式; 3

学会使用VHDL 语言进行可编程逻辑器件的逻辑设计; 4

掌握通用阵列逻辑GAL 的编程、下载、验证功能的全部过程

二、实验原理 1

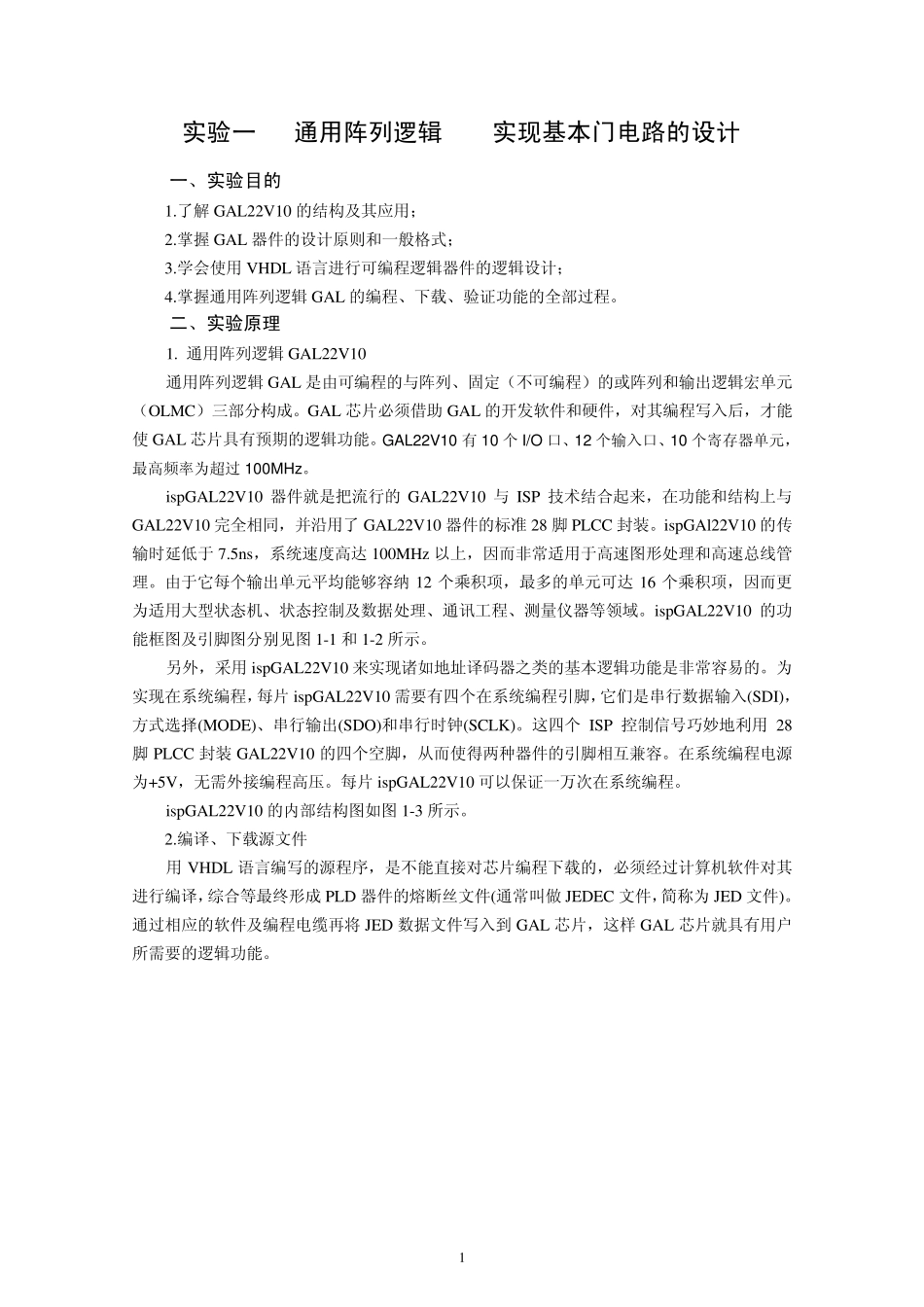

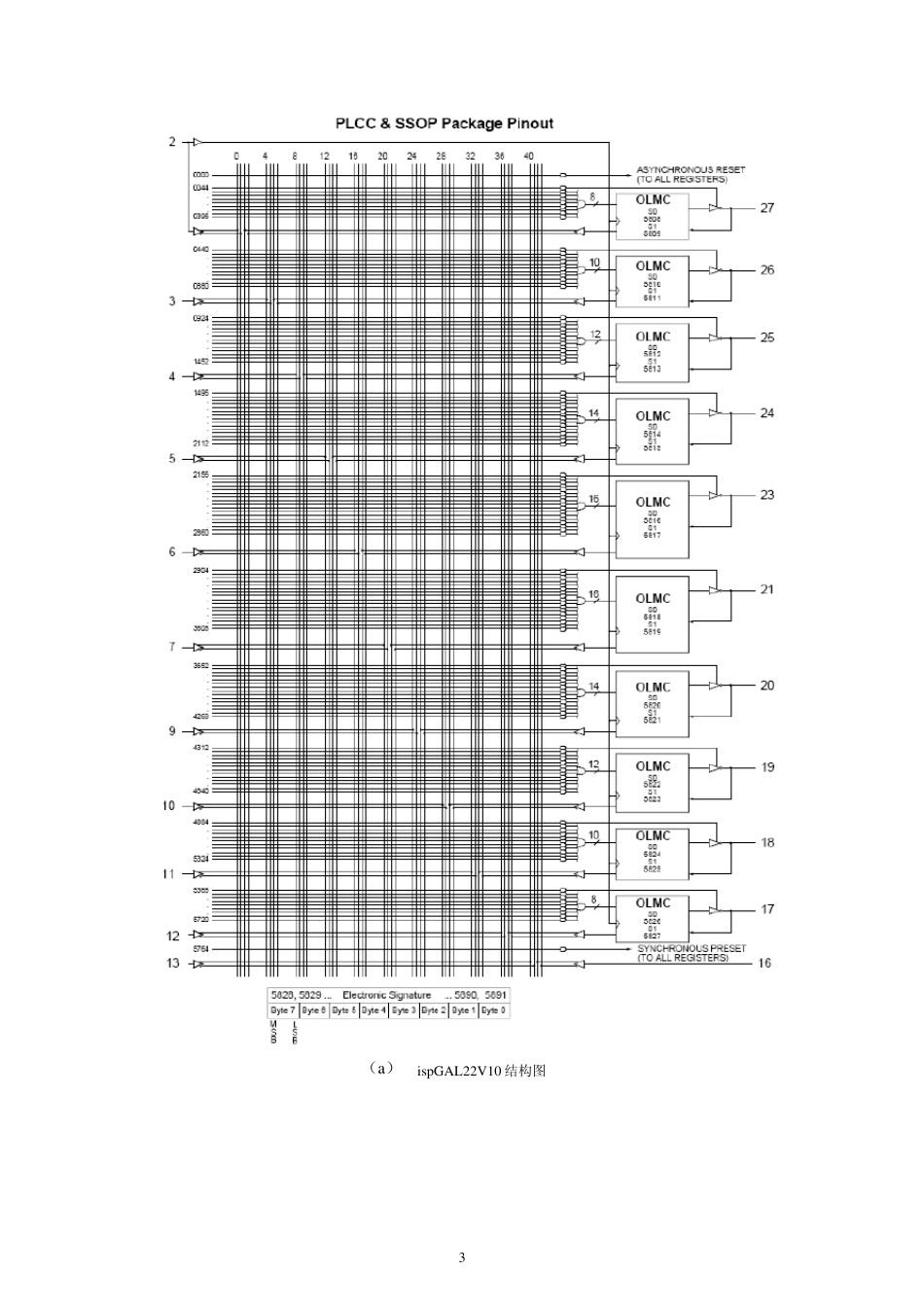

通用阵列逻辑GAL22V10 通用阵列逻辑GAL 是由可编程的与阵列、固定(不可编程)的或阵列和输出逻辑宏单元(OLMC)三部分构成

GAL 芯片必须借助 GAL 的开发软件和硬件,对其编程写入后,才能使GAL 芯片具有预期的逻辑功能

GAL22V10 有 10 个 I/O 口、12 个输入口、10 个寄存器单元,最高频率为超过 100MHz

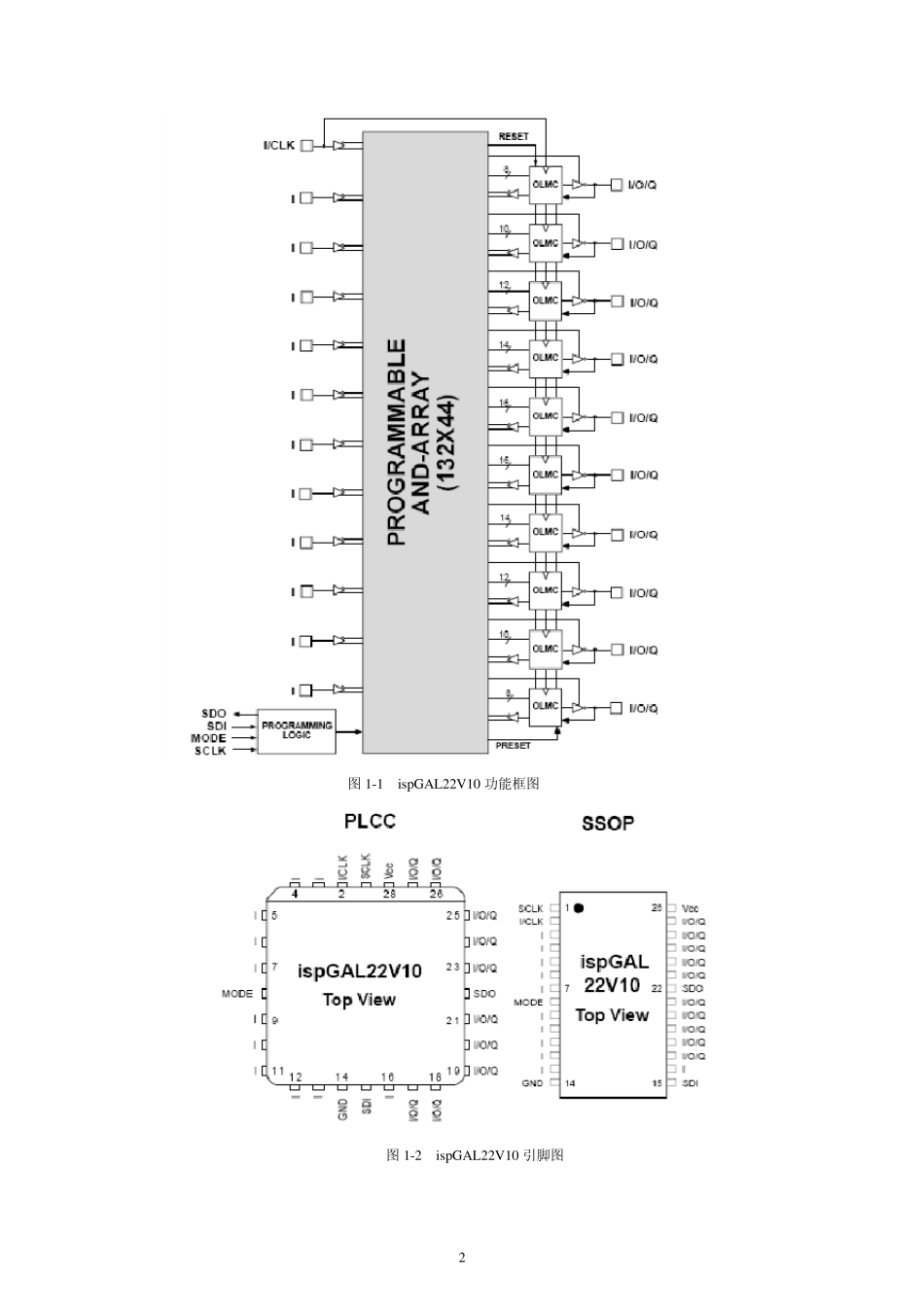

ispGAL22V10 器件就是把流行的GAL22V10 与 ISP 技术结合起来,在功能和结构上与GAL22V10 完全相同,并沿用了GAL22V10 器件的标准 28 脚 PLCC 封装

ispGAl22V10 的传输时延低于 7

5ns,系统速度高达 100MHz 以上,因而非常适用于高速图形处理和高速总线管理

由于它每个输出单元平均能够容纳 12 个乘积项,最多的单元可达 16 个乘积项,因而更为适用大型状态机、状态控制及数据处理、通讯工程、测量仪器等领域

ispGAL22V10 的功能框图及引脚图分别见图 1-1 和1-2 所示

另外,采用ispGAL22V10 来实现诸如地址译码器之类的基本逻辑功能是非常容易的

为实现在系统编程,每片 ispGAL22V10 需要有四个在系统编程引脚,它们是串行数据输入(SDI),方式选择(MODE)、串行输出(SDO)和串行时钟(SCLK)

这四个 ISP 控制信号巧妙地利用28脚 PLCC 封装 GAL22V10 的四个空脚,从而使得两种器件的引脚相互兼容

在系统编程电源为+5V,无需外接编