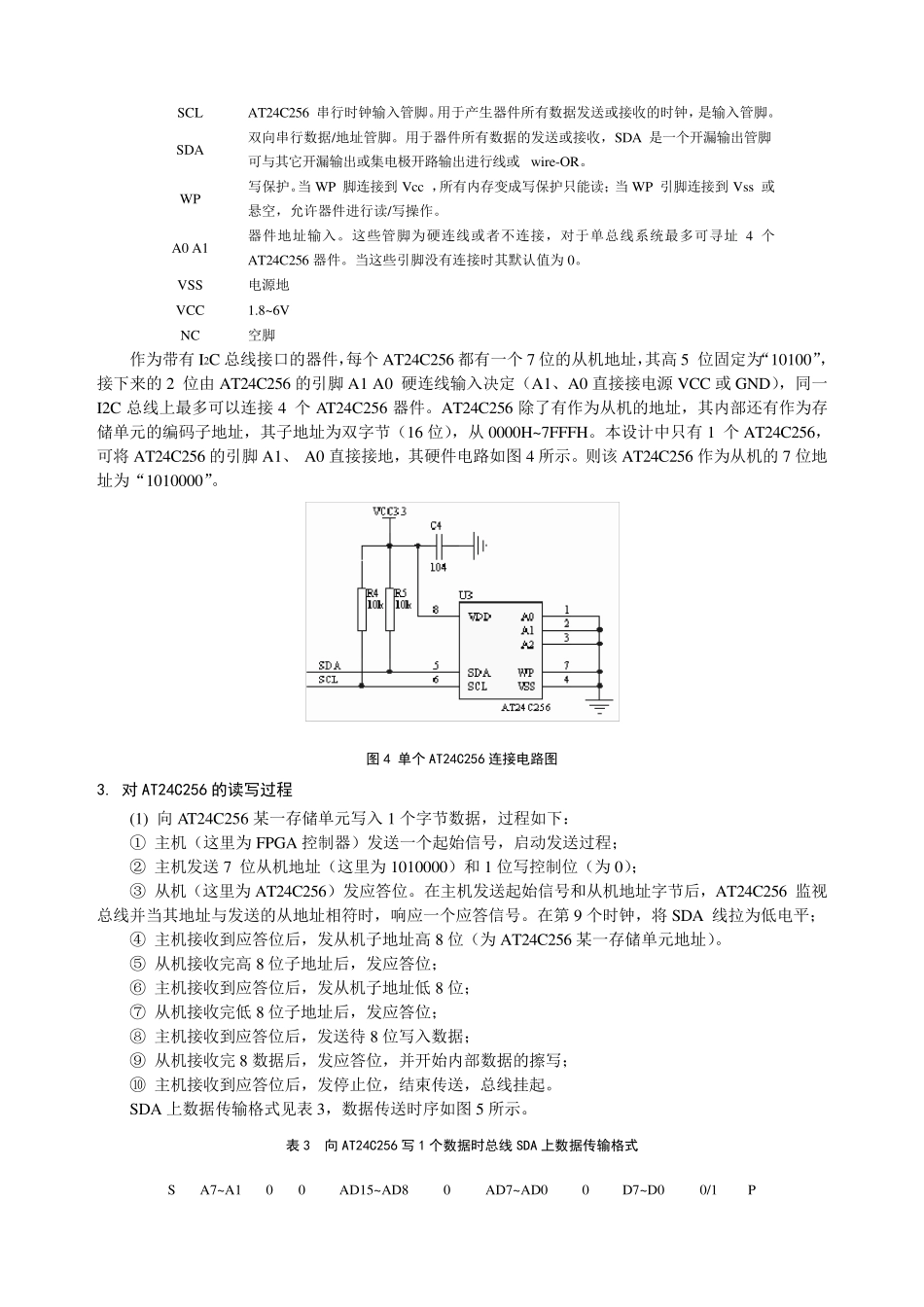

FPGA 与I2C 总线器件接口电路设计 利用FPGA 模拟I2C 总线协议对I2C 总线接口器件AT24C256 进行读写操作

利用按键输入读写命令和相应的地址、数据,对芯片进行读写操作,读写的数据用数码管显示

一、I2C 总线接口电路设计分析 1

I2C 总线协议 I2C 总线的两根通信线,一根是串行数据线SDA,另一根是串行时钟线SCL

多个符合 I2C 总线标准的器件都可以通过同一条 I2C 总线进行通信,而不需要额外的地址译码器

每个连接到总线上的器件都有一个唯一的地址作为识别的标志,都可以发送或接收数据

I2C 总线通信速率受主机控制,标准模式下可达 100kbit/s

一般具有 I2C 总线的器件其 SDA、SCL 引脚都为集电极(或漏极)开路结构

因此实际使用时,SDA和SCL 信号线必须加 3~ 10K 的上拉电阻

总线空闲时均保持高平

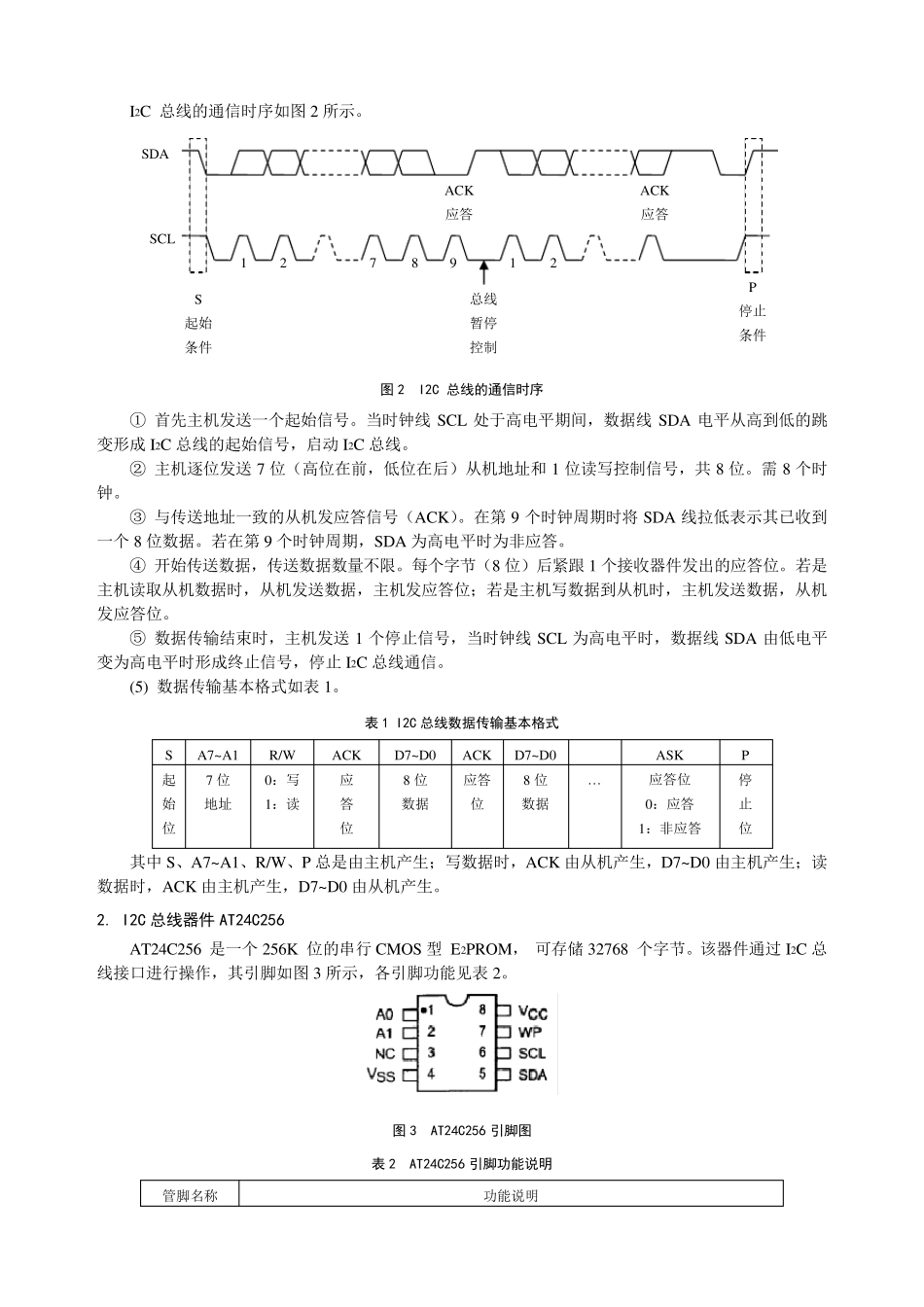

I2C 总线接法如图1 所示

图 1 I2C 总线连接示意图 (1) I2C 的主机和从机,发送器和接收器 产生I2C 总线时钟信号和起始、停止控制信号的器件,称为主机,被主机寻址的器件称为从机

任何将数据传送到 I2C 总线的器件称为发送器,任何从I2C 总线接收数据的器件称为接收器

主机和从机都可作为发送数据器件和接收数据器件

(2) I2C 总线上数据的有效性: 时钟线SCL 为高电平时,数据线SDA 的任何电平变化将被看作总线的起始或停止信号; 在数据传送过程中,当时钟线SCL 为高电平时,数据线SDA 必须保持稳定状态 ,不允 许 有跳 变;数据线SDA 的状态 只 能 在SCL 低 电平期 间 才 能 改 变

即 进行串行传送数据时,在SCL 高电平期 间 传送位 数据,低 电平期 间 准备 数据

(3) 从机地址 I2C 总线不需要额外的片选 信号或地址译码

多个 I2C 总线接口器件可连接到