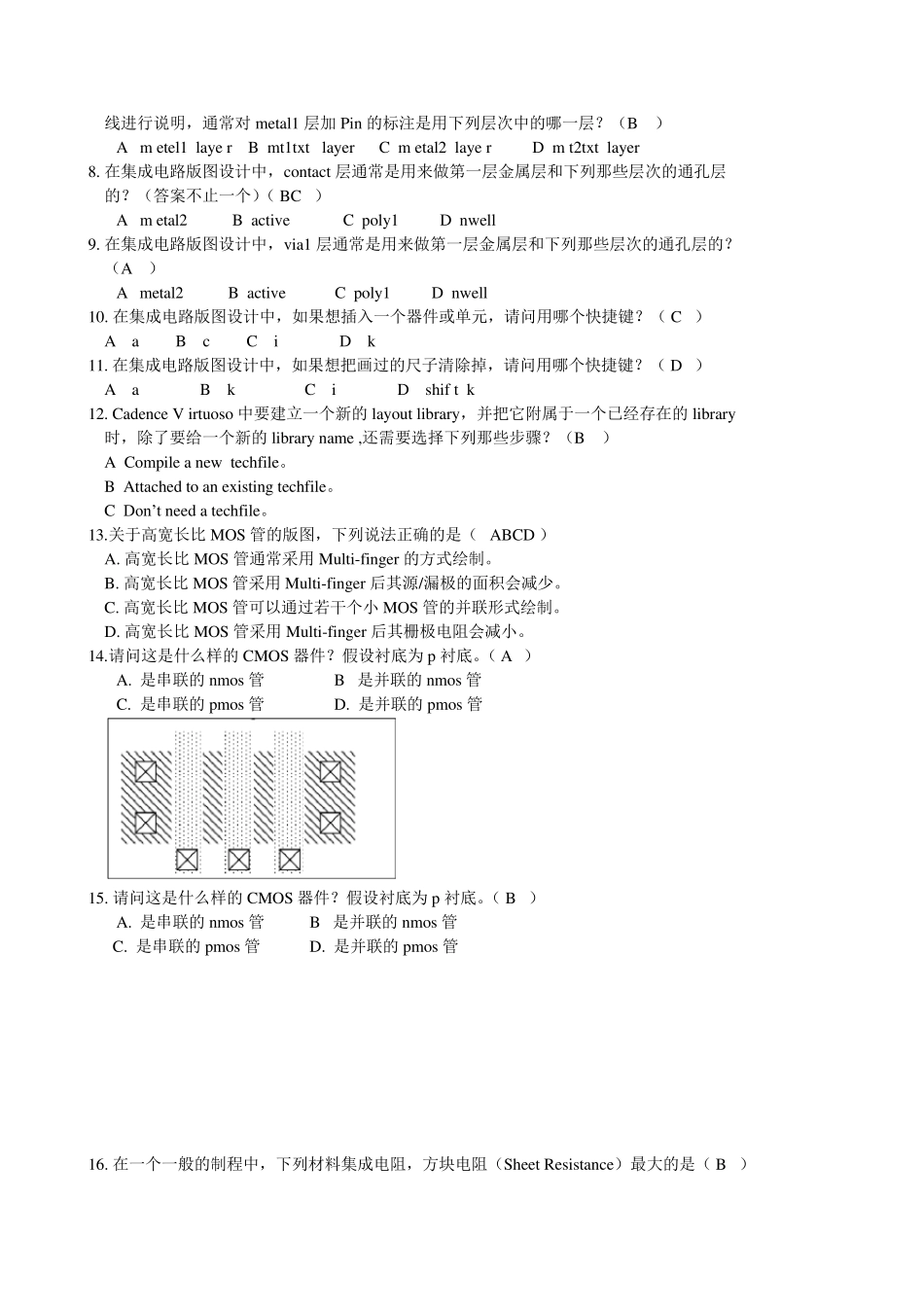

IC 工艺及版图设计分类习题 Ⅰ 填 空 题 1. 有 一 种 称 为 0.13u m 2P5M CMOS 单 阱 工 艺 , 它 的 特 征 线 宽 为 0.13u m , 互 连 层 共 有 7 层 , 其 电 路 类 型 为 CMOS 。 2. 某 种 工 艺 称 为 0.35u m Mix ed Signal 2P4M Poly cide 3.3VProcess, 请 判 断 其 特 征 尺 寸 为 0.35u m , 互 连 层 共 有 6 层 , 适 合 ( 适 合 或 不 适 合 ) 于 设 计 模 拟 电 路 。 3. 请 根 据 实 际 的 制 造 过 程 排 列 如 下 各 选 项 的 顺 序 : a. 生 成 多 晶 硅 b. 确 定 阱 的 位 置 和 大 小 c. 定 义 扩 散 区 , 生 成 源 漏 区 d. 确 定 有 源 区 的 位 置 和 大 小 e. 确 定 接 触 孔 位 置 正 确 的 顺 序 为 : bdace 。 4. N 阱 CMOS 工 艺 中 ,之 所 以 要 将 衬 底 接 GND 、阱 接 到 电 源 上 ,是 因 为 阱 和 衬 底 构 成 的 pn 节 反 偏 。 5. 版 图 验 证 主 要 包 括 三 方 面 : LVS , DRC , ERC ; 完 成 该 功 能 的 Cadence 工 具 主 要 有 ( 列 举 出 两 个 ): DIVA , DRACULA 。 6. 芯 片 使 用 0.01 cmΩi P 型 衬 底 顶 部的 8u m 厚的 10 cmΩi P 型 外延层 制 作, 计 算从芯 片 抽取 25mA 电 流需要 6.67×104 u m2 衬 底 接 触 面 积。 假设 最大 允许的 衬 底 去偏 置 为 0.3V。 7.某 种 铜铝合 金可以 安全工 作于 5×1 05 A/ cm2 的 电 流密度下 。 如 果金属层 厚度为 8000Ao, 则10u m 宽 的 金属连 线 能 承受 40 mA 的 电 流;当 通 过 氧 化 台 阶 时 , 金属层 厚度减 小 了 50%, 则该 10u m 宽 的 金属连 线 能 承受 20 mA 电 流。 8. CMOS 工 艺 中 集 成 电 路 中 的 电 阻 主 要 有 __电 阻 , 扩 散 电 阻 , poly 电 阻 _三 种 。 9.CMOS 工 艺 中 某 种 材 料 工 艺 变 化 方 块 电 阻 偏 差 在 2 0 % , 假设 特 征 尺 寸 为0.5u m,工 艺 线 宽 控 制 维 持 在10%以 内 。 假设 使 用 1u m 的 线 宽 ...