2 基于ISE 的仿真 在代码编写完毕后,需要借助于测试平台来验证所设计的模块是否满足要求

ISE 提供了两种测试平台的建立方法,一种是使用HDL Bencher 的图形化波形编辑功能编写,另一种就是利用HDL 语言

由于后者使用简单、功能强大,所以本节主要介绍基于Verolog 语言的测试平台建立方法

1.测试波形法 在ISE 中创建testbench 波形,可通过 HDL Bencher 修改,再将其和仿真器连接起来,再验证设计功能是否正确

首先在工程管理区将 Sources for 设置为 Behavioral Simulation,然后在任意位置单击鼠标右键,在弹出的菜单中选择“New Source”命令,然后选中“Test Bench WaveForm”类型,输入文件名为“test_bench”,点击 Next 进入下一页

这时,工程中所有Verilog Module 的名称都会显示出来,设计人员需要选择要进行测试的模块

由于本工程只有一个模块,所以只列出了test,如图4-30 所示

图4-30 选择待测模块对话框 用鼠标选中 test,点击“Next”后进入下一页,直接点击“Finish”按键

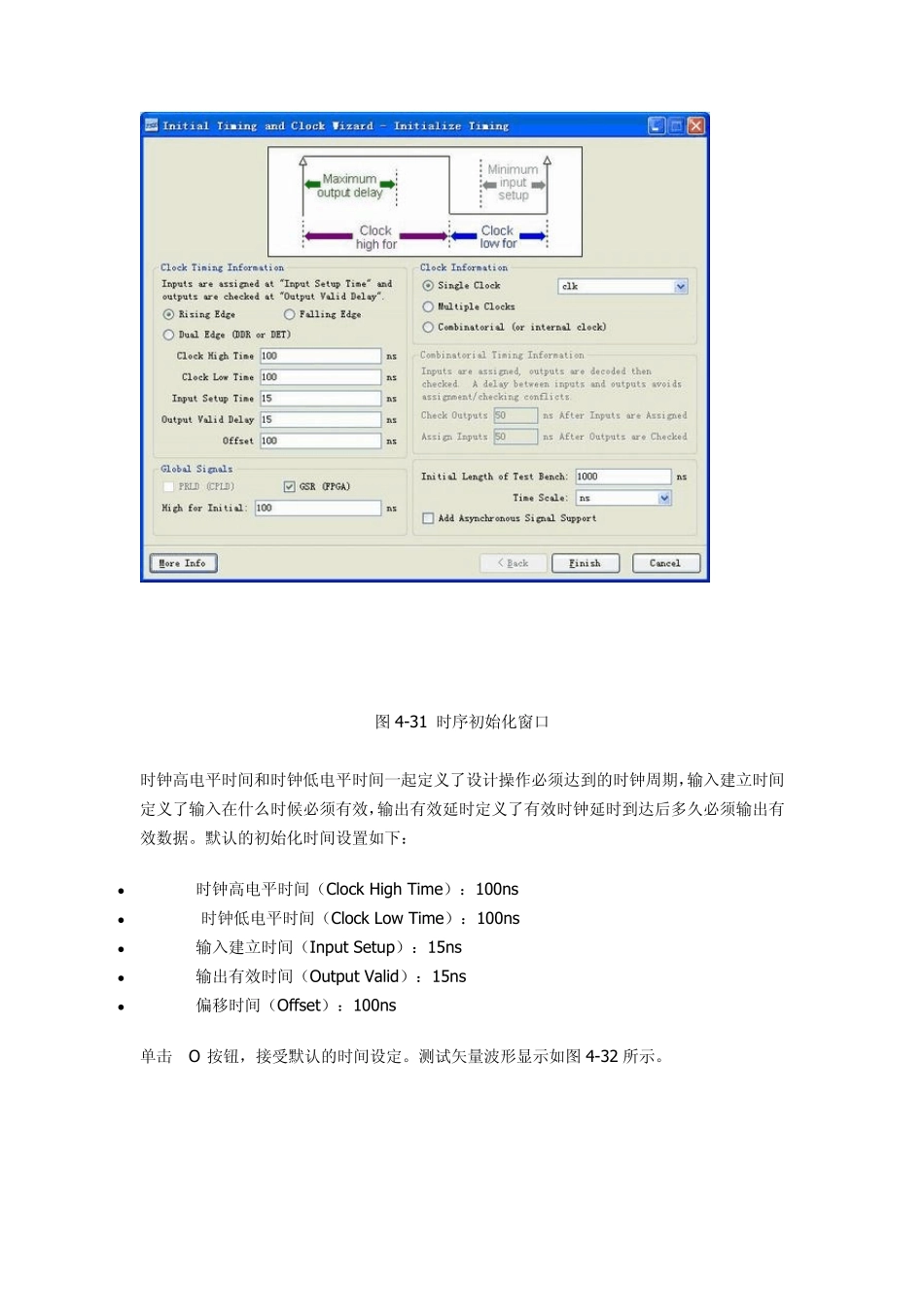

此时 HDL Bencher 程序自动启动,等待用户输入所需的时序要求,如图4-31 所示

图4-31 时序初始化窗口 时钟高电平时间和时钟低电平时间一起定义了设计操作必须达到的时钟周期,输入建立时间定义了输入在什么时候必须有效,输出有效延时定义了有效时钟延时到达后多久必须输出有效数据

默认的初始化时间设置如下: 时钟高电平时间(Clock High Time):100ns 时钟低电平时间(Clock Low Time):100ns 输入建立时间(Input Setup):15ns 输出有效时间(Output Valid):15ns 偏