第 1 页 共5 页 电科《集成电路原理》期末考试试卷 一、填空题 1

(1分) 年,第一次观测到了具有放大作用的晶体管

2.(2分)摩尔定律是指

集成电路按工作原理来分可分为 、 、

(4分)光刻的工艺过程有底膜处理、涂胶、前烘、 、 、 、 和去胶

( 4分 ) MOSFET 可 以分为 、 、 、 四种基本类型

(3分)影响 MOSFET阈值电压的因素有: 、 以及

(2分)在 CMOS反相器中,Vin,Vout分别作为PMOS和 NMOS的 和 ; 作为PMOS的源极和体端, 作为NMOS的源极和体端

8.(2分)CMOS逻辑电路的功耗可以分为 和

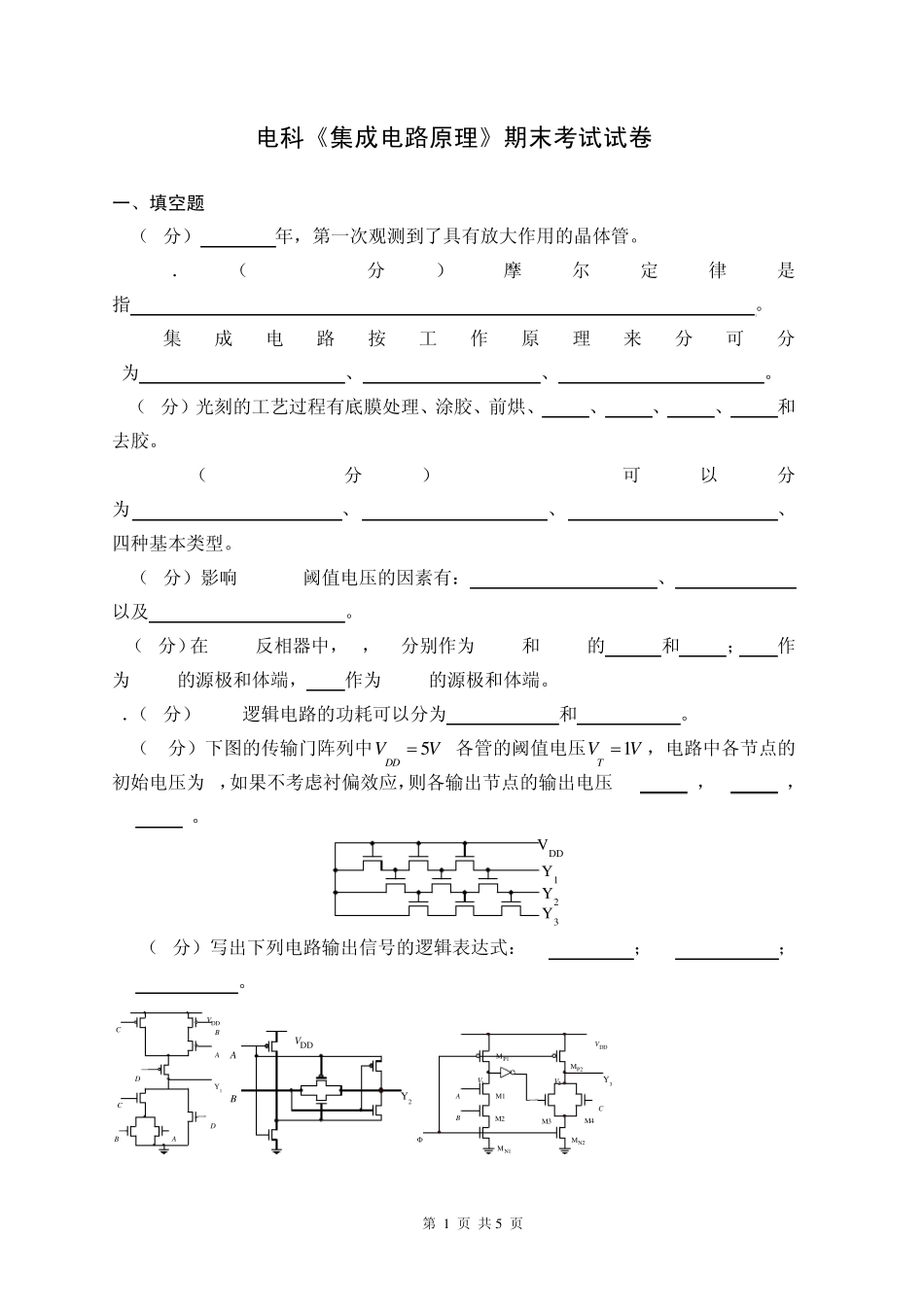

(3分)下图的传输门阵列中5DDVV,各管的阈值电压1TVV,电路中各节点的初始电压为0,如果不考虑衬偏效应,则各输出节点的输出电压 Y1= V,Y2= V,Y3= V

V DDY 1Y 3Y 2 10

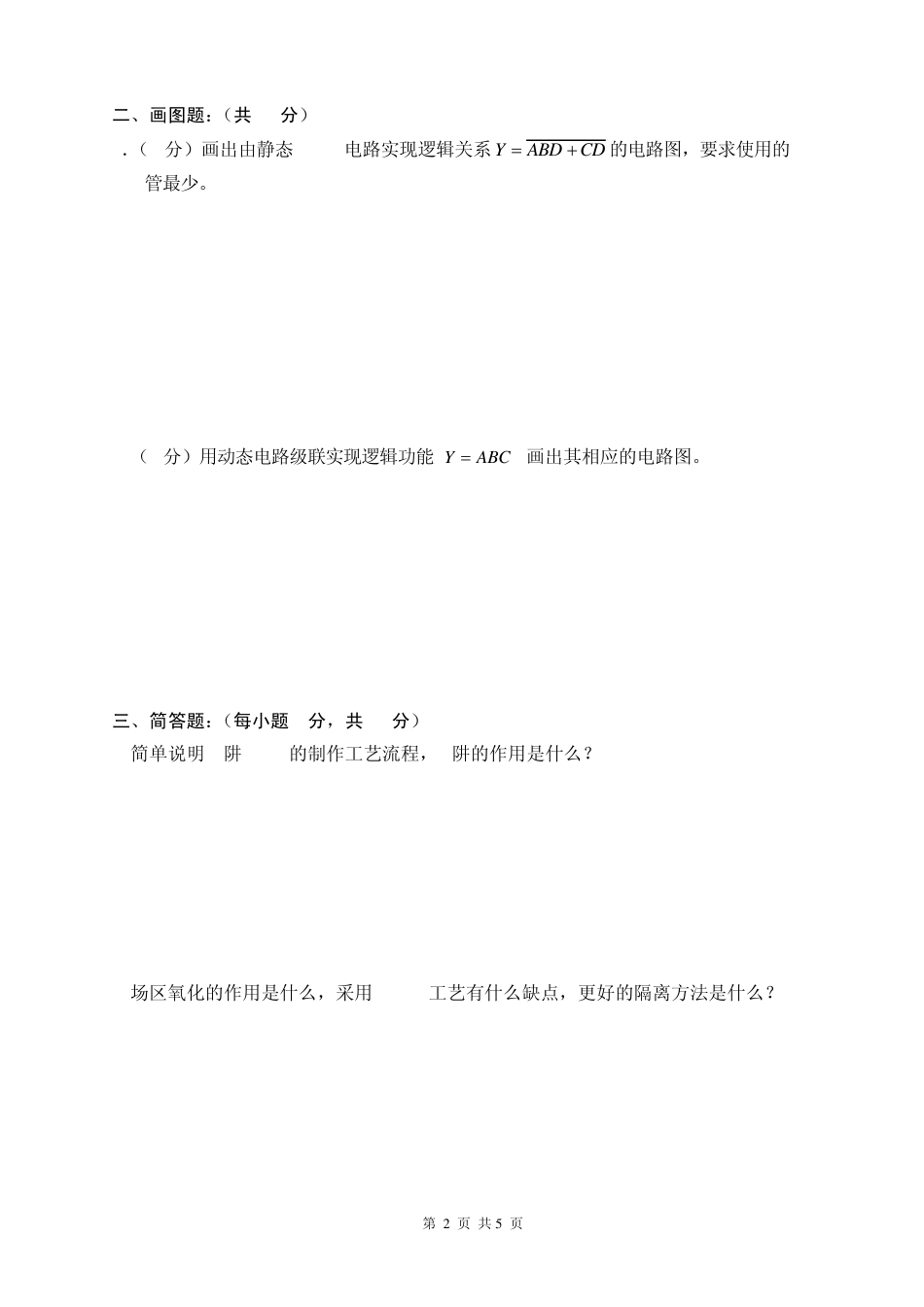

(6分)写出下列电路输出信号的逻辑表达式:Y1= ;Y2= ;Y3=

AABBCCDDVDDY 1VDDABY 2ABM1M2VDDM3M4CVV12MMMMP1P2N1N2Y 3 第 2 页 共5 页 二、画图题:(共 12分) 1.(6分)画出由静态CMOS电路实现逻辑关系YABDCD的电路图,要求使用的MOS管最少

(6分)用动态电路级联实现逻辑功能 YABC,画出其相应的电路图

三、简答题:(每小题 5分,共 20分) 1

简单说明 n阱 CMOS的制作工艺流程,n阱的作用是什么

场区氧化的作用是什么,采用LOCOS工艺有什么缺点,更好的隔离方法是什么

第 3 页 共5 页 3

简述静态CMOS电路的优点

简述动态电路的优点和存在的问题

四、分析设计题:(共 38分 1

(12分)考虑标准0

13m CMOS工艺下NMO