下载后可任意编辑 本科实验报告实验名称: 可编程逻辑器件实验报告 课程名称:可编程逻辑器件实验时间:任课老师:实验地点:实验老师:实验类型:□ 原理验证■ 综合设计□ 自主创新学生姓名:学 号 / 班级:组 号:下载后可任意编辑学 院:同组搭档:专 业:成 绩:9999 计数器一、实验目的编程实现一个含清零功能 9999 计数器,并用 7 段数码管显示

二、实验器材EPM7128STC100-15,计算机下载后可任意编辑三、实验过程(1)原理分析a、分频要实现一个 0-9999 计数器,并且肉眼可观,但是 EPM7128STC100-15 系统只有一个 6M的时钟,频率太高,肉眼不可见,因此得用一个分频器将系统时钟降下来

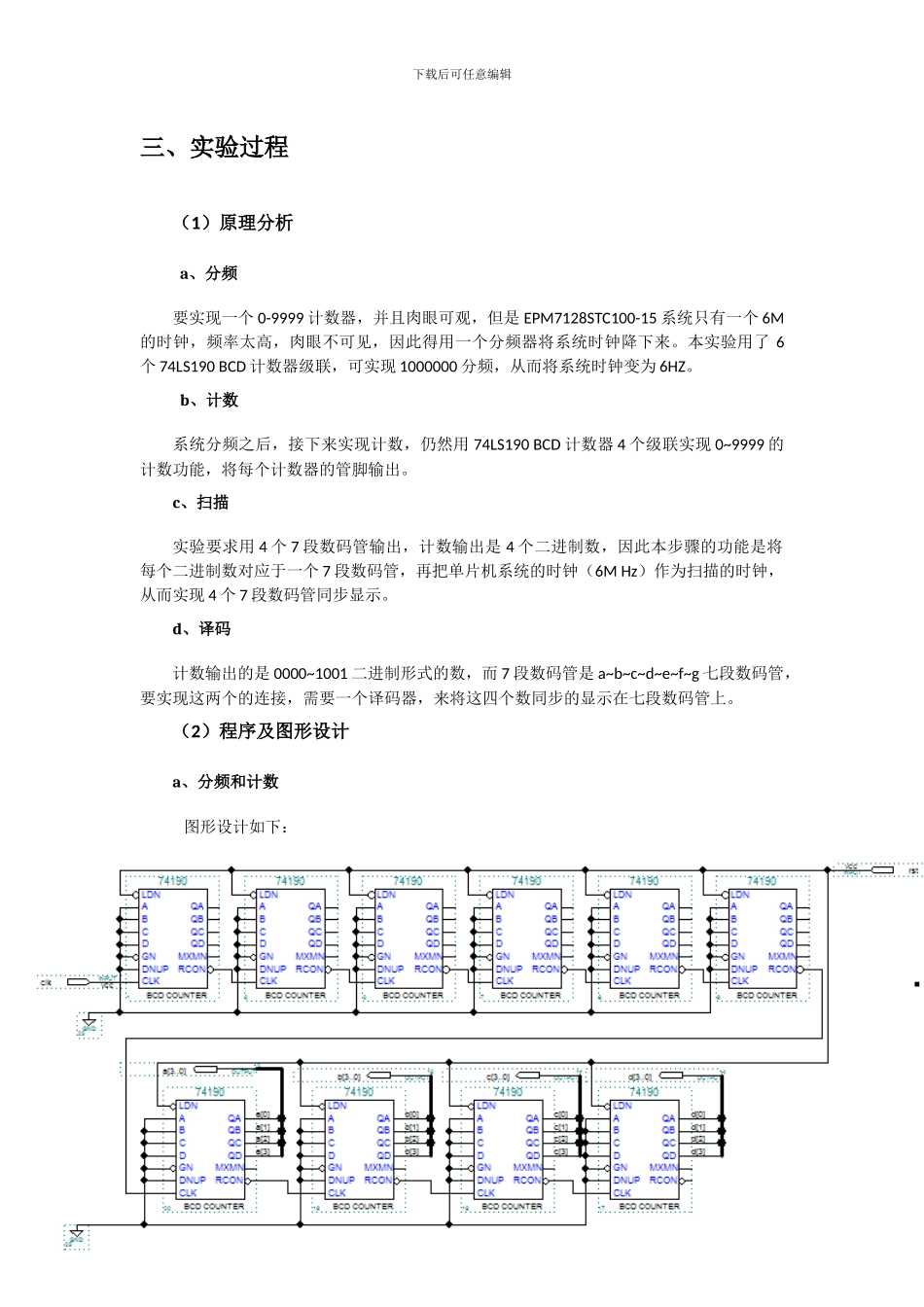

本实验用了 6个 74LS190 BCD 计数器级联,可实现 1000000 分频,从而将系统时钟变为 6HZ

b、计数系统分频之后,接下来实现计数,仍然用 74LS190 BCD 计数器 4 个级联实现 0~9999 的计数功能,将每个计数器的管脚输出

c、扫描实验要求用 4 个 7 段数码管输出,计数输出是 4 个二进制数,因此本步骤的功能是将每个二进制数对应于一个 7 段数码管,再把单片机系统的时钟(6M Hz)作为扫描的时钟,从而实现 4 个 7 段数码管同步显示

d、译码计数输出的是 0000~1001 二进制形式的数,而 7 段数码管是 a~b~c~d~e~f~g 七段数码管,要实现这两个的连接,需要一个译码器,来将这四个数同步的显示在七段数码管上

(2)程序及图形设计a、分频和计数 图形设计如下:下载后可任意编辑画好上面的图以后编译后再将上面的设计为一整个芯片,如下图所示:b、扫描 代码:--********************************************LIBRARY IEEE;USE IEEE

STD_LOGIC_