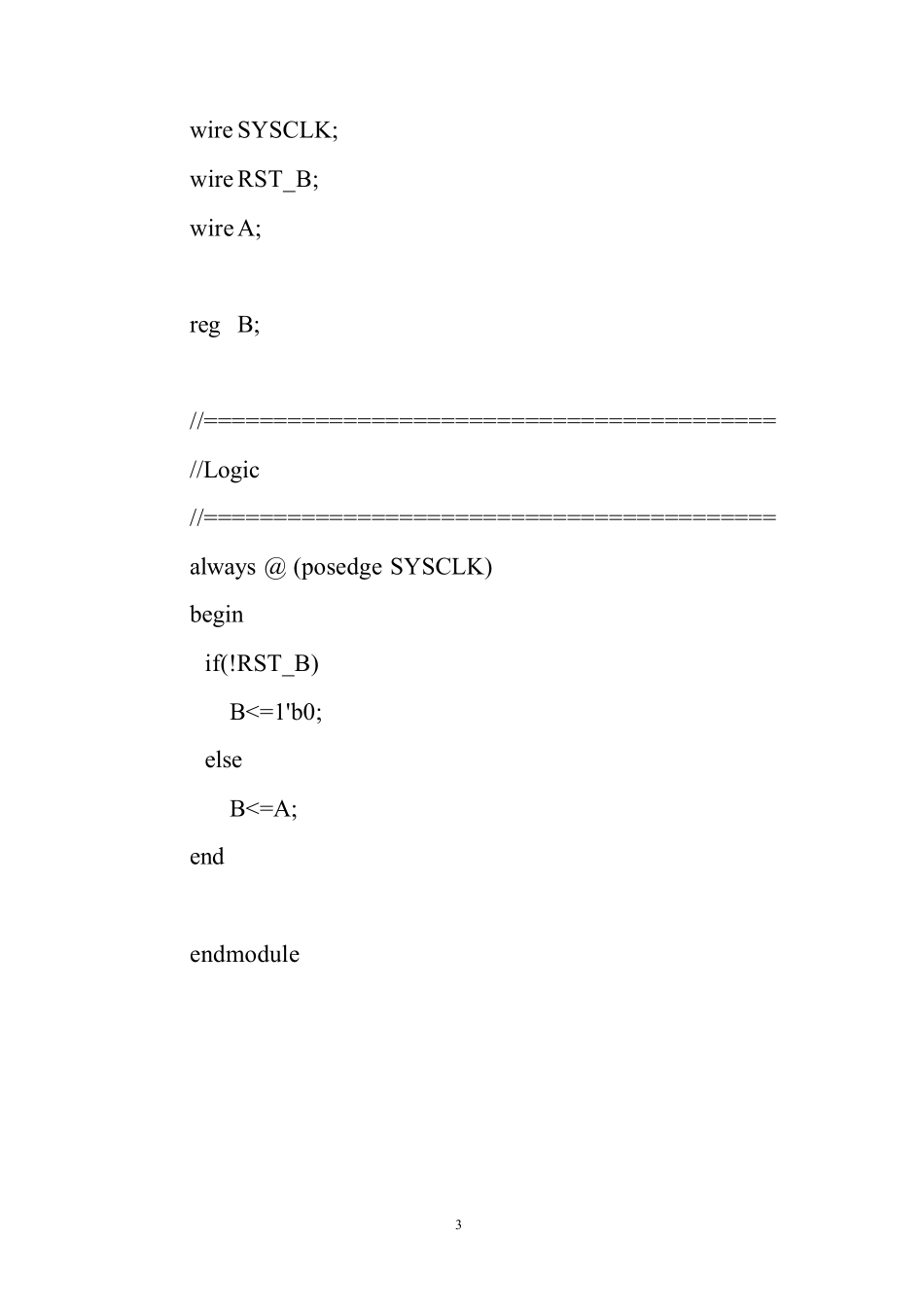

1针对数字系统的设计,我们经常会遇到复位电路的设计,对初学者来说不知道同步复位与异步复位的区别与联系,今天我对这个问题简要的阐述下,希望对初学者有一定的参考意义,若有不正确的地方愿大家明示。同步复位原理:同步复位只有在时钟沿到来时复位信号才起作用,则复位信号持续的时间应该超过一个时钟周期才能保证系统复位。异步复位原理:异步复位只要有复位信号系统马上复位,因此异步复位抗干扰能力差,有些噪声也能使系统复位,因此有时候显得不够稳定,要想设计一个好的复位最好使用异步复位同步释放。同步复位与异步复位的优劣:异步复位消耗的 PFGA 逻辑资源相对来说要少些,因此触发器自身带有清零端口不需要额外的门电路,这是其自身的优势,通常在要求不高的情况下直接使用异步复位就 OK。下面我用 verilog 来演示下同步复位与异步复位。同步复位的 verilog 程序如下:module D_FF(2//Inpu t portsSYSCLK,RST_B,A,//Ou tpu t portsB);//=========================================//Inpu t and ou tpu t declaration//=========================================inpu tSYSCLK;inpu tRST_B;inpu tA;ou tpu t B;//=========================================//Wire and reg declaration//=========================================3wire SYSCLK;wire RST_B;wireA;reg B;//=========================================//Logic//=========================================always @ (posedge SYSCLK)beginif(!RST_B)B<=1'b0;elseB<=A;endendmodule4综合后的 RTL 级电路图如下:异步复位的 verilog 程序如下:module D_FF(//Input portsSYSCLK,RST_B,A,//Output portsB);//=========================================//Input and output declaration//=========================================inputSYSCLK;inputRST_B;5inputA;output B;//=========================================//Wire and reg declaration//=========================================wire SYSCLK;wire RST_B;wireA;reg B;//=========================================//Logic//=========================================always @ (posedge SYSCLK or negedge RST_B)beginif(!RST_B)B<=1'b0;else6B<=A;endendmodule综合后的 RTL 级电路图如下:通过比较显然异步复位消耗的逻辑资源要少些,因此通常的设计中都采用异步复位的方式,需要进一步的学习的话,可以再研究下其它的资料。