第6 章 触发器 【6-1】已知由与非门构成的基本RS 触发器的直接置“0”端和直接置“1”端的输入波形如图6

1 所示,试画出触发器Q 端和Q 端的波形

RdSdQQ 图 6

1 解: 基本RS 触发器Q 端和Q 端的波形可按真值表确定,要注意的是,当dR 和dS 同时为“0”时,Q 端和Q 端都等于“1”

dR 和dS 同时撤消,即同时变为“1”时,Q 端和Q 端的状态不定

1(b)所示,图中 Q 端和Q 端的最右侧的虚线表示状态不定

RdS dQQ不定状态 图6

1(b) 题 6-1 答案的波形图 【6-2】触发器电路如图6

2(a)所示,在图(b)中画出电路的输出端波形,设触发器初态为“0”

QQRdSddSdQQR (a) (b) 图6

2 解: 此题是由或非门构成的RS 触发器,工作原理与由与非门构成的基本RS 触发器一样,只不过此电路对输入触发信号是高电平有效

参照题 6-1 的求解方法,即可画出输出端的波形,见图6

dS dQQR不定状态 图6

2(c) 【6-3】试画出图6

3 所示的电路,在给定输入时钟作用下的输出波形,设触发器的初态为“0”

C11J1KRSQ“1”CPYZ CP 图 6

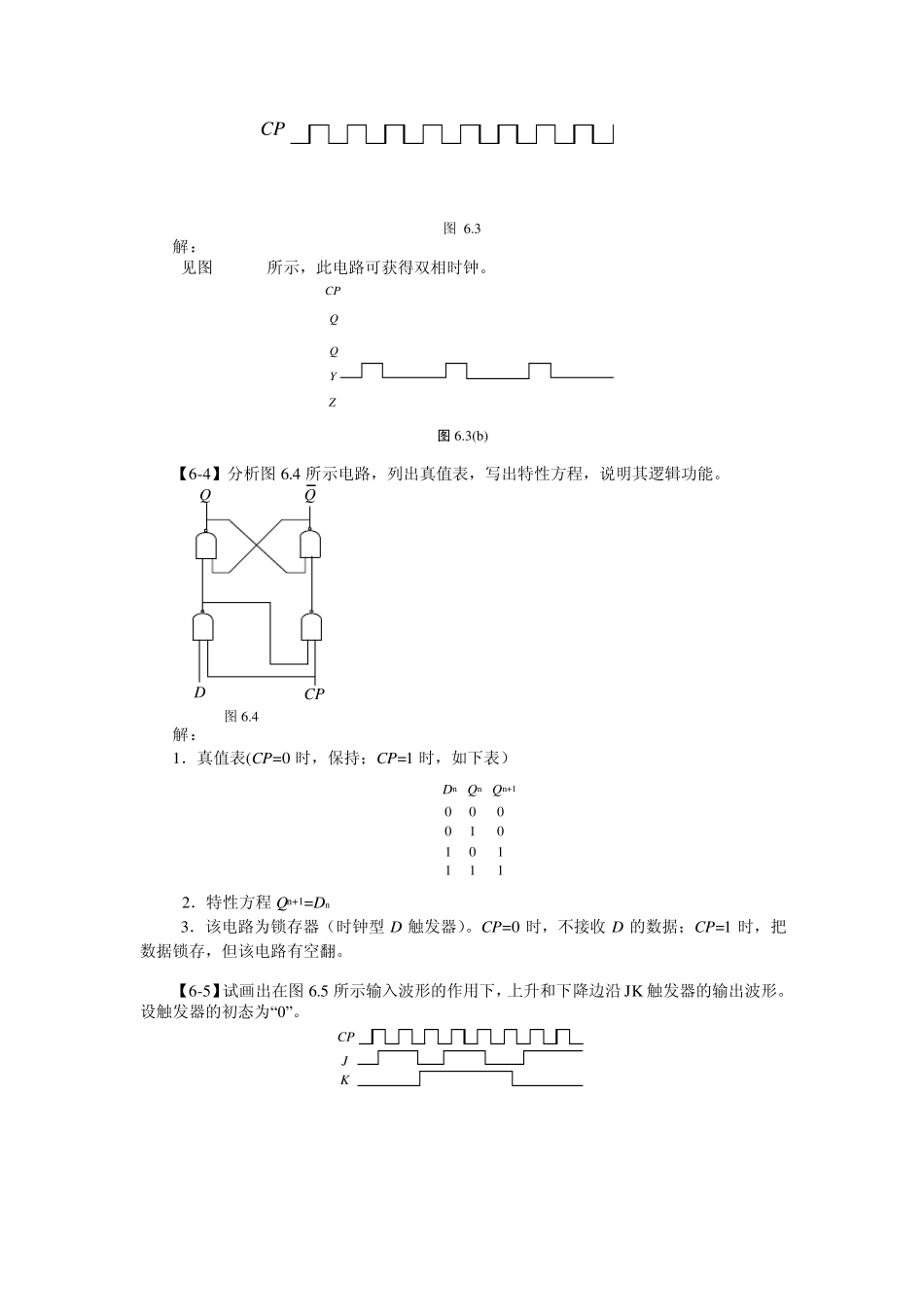

3 解: 见图6

3(b)所示,此电路可获得双相时钟

QQCPYZ 图6

3(b) 【6-4】分析图6

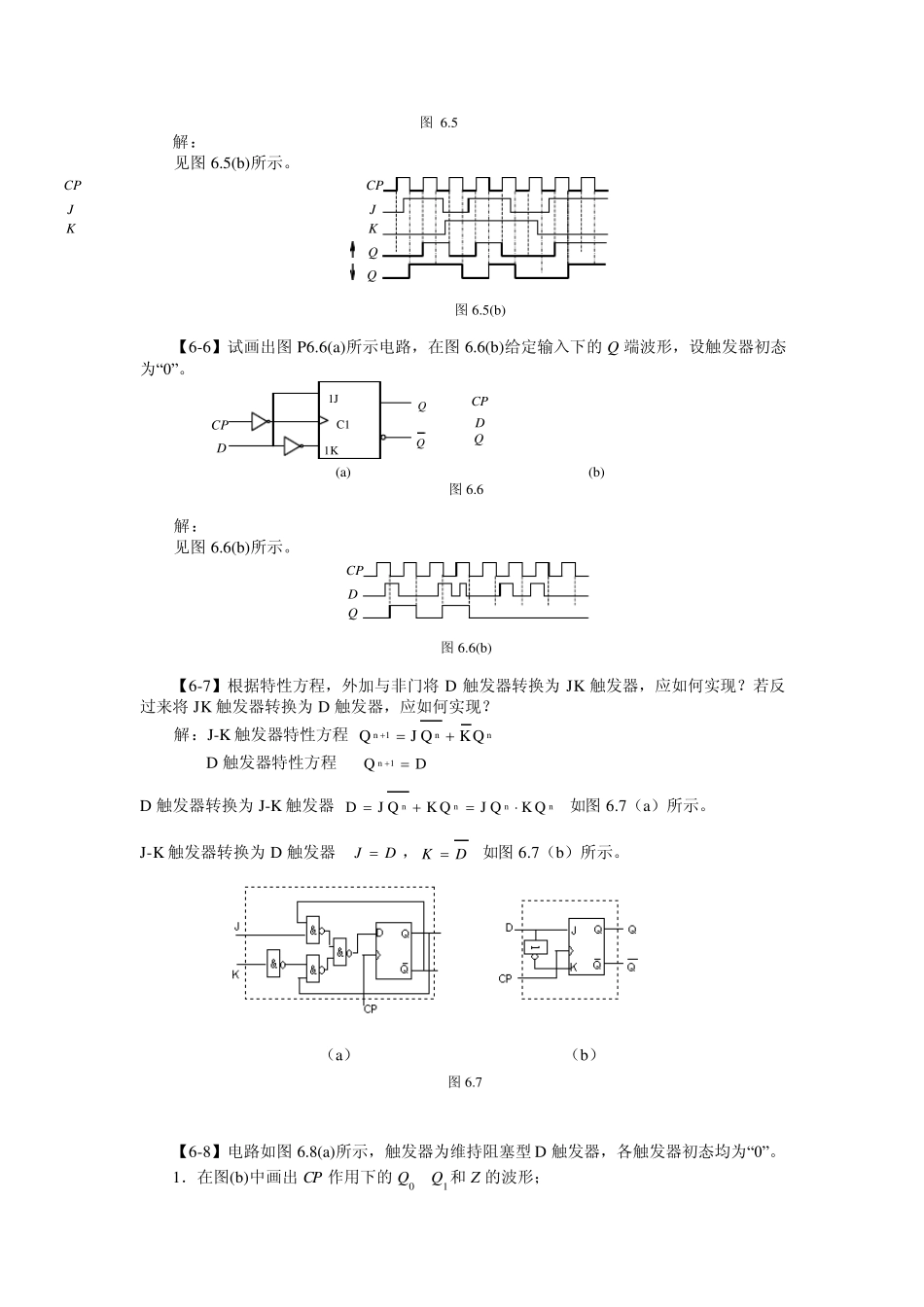

4 所示电路,列出真值表,写出特性方程,说明其逻辑功能

QQDCP 图6

4 解: 1.真值表(CP=0 时,保持;CP=1 时,如下表) Dn Qn Qn+1 0 0 0 0 1 0 1 0 1 1 1 1 2.特性方程 Qn+1=Dn 3.该电路为锁存器(时钟型 D 触发器)

CP=0 时,不接收 D 的数据;CP=1 时,把数据锁存,但该电路有空翻

【6-5】试画出在图6

5 所示输入波形的作用下,上升和下降边沿 JK 触发器