实验一 Qu artu s II 工具使用 一、 实验目的 1

掌握 Quartus II 的开发界面和开发流程; 2

掌握用原理图方法进行电路设计; 3

经过比较了解利用verilog 语言进行电路设计的优点; 4

学会对设计电路进行波形功能仿真

二、 实验设备 1

安装 Quartus II 软件的计算机 2

SmartEDA 实验箱 三、 实验内容 1

打开 Quartus II 工作环境,如图 1 所示

图 1 打开 Quartus II 工作环境 2

新建一个 Quartus 工程,在 File 菜单中选择 New Project Wizard 帮助新建工程

打开 Wizard 之后,界面如图 2 所示

点击 Next,输入工程工作路径、工程文件名以及顶层实体名

注意:这里输入的顶层实体名字必须与之后设计文件(比如

v 文件)的顶层模块名相同,默认实体名与工程文件名相同,本次实验采用这种命名方法,当然用户也可以根据需要输入不同的实体名

工作路径:E:\yourname\decode_38 //yourname 用个人姓名全拼替换 工程文件名:decode_38 顶层实体名:decode_38 输入结束后如图 3 所示

输入结束后点击 Next

图2 New Project Wizard 界面 图3 输入设计工程信息 3

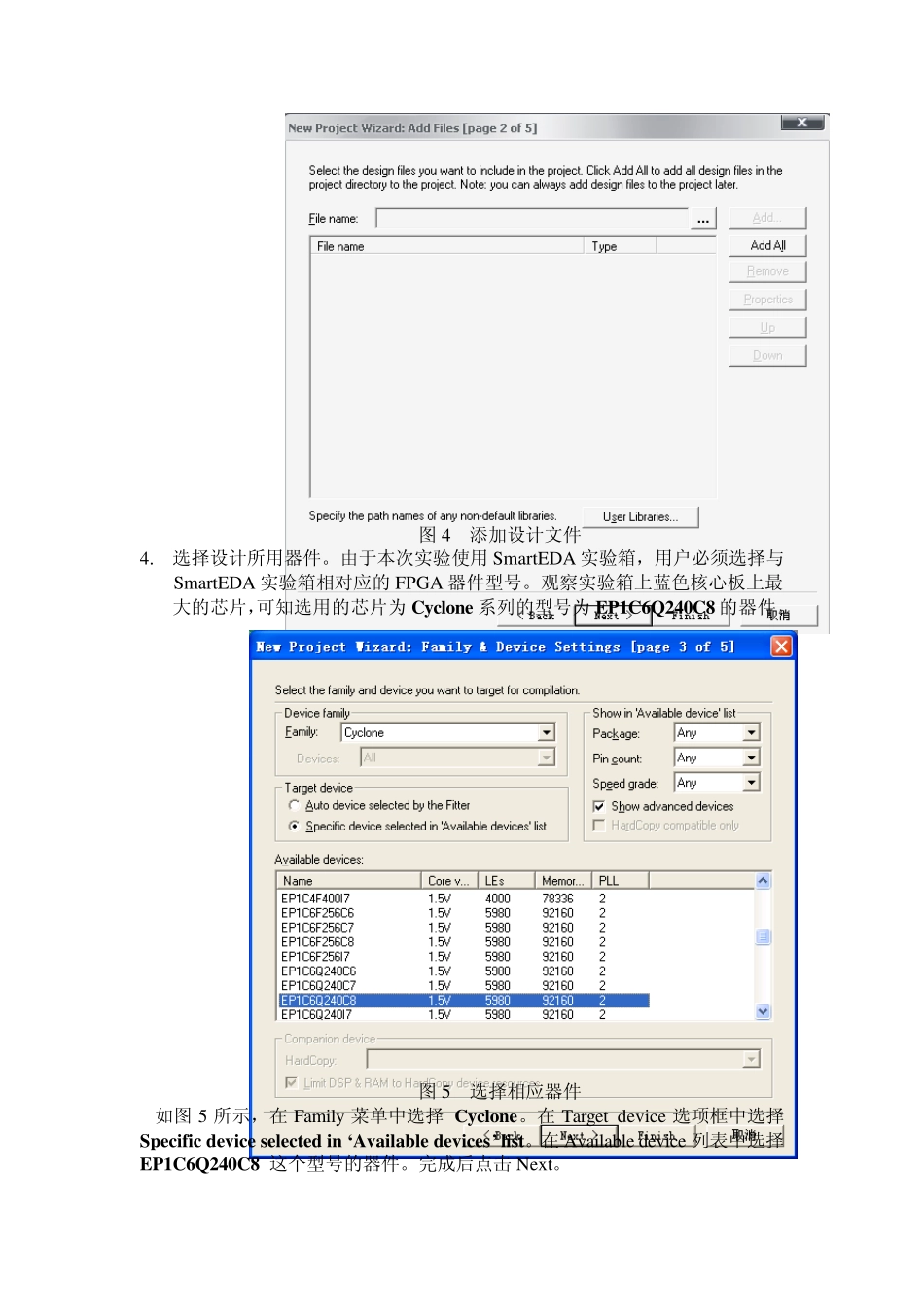

添加设计文件,界面如图4 所示

如果用户之前已经有设计文件(比如

v 文件),那么再次添加相应文件; 如果没有完成的设计文件,点击 Next,之后添加并且编辑设计文件

图4 添加设计文件 4

选择设计所用器件

由于本次实验使用SmartEDA 实验箱,用户必须选择与SmartEDA 实验箱相对应的 FPGA 器件型号

观察实验箱上蓝色核心板上最大的芯片,可知选用的芯片为 Cyclone 系列的型号为 EP1C6Q2