实验二 基本门电路逻辑功能的测试 一、实验目的 1.熟悉能主要门电路的逻辑功; 2.掌握基本门电路逻辑功能的测试方法

二、使用仪器 DZX-2B 型电子学综合实验装置(简称实验台)

三、实验原理 1 集成电路芯片介绍 主要的门电路包括与非门、或非门和与或非门

在数字电路中广泛应用

无论大规模集成电路多么复杂,但内部也还是由这些基本门电路构成,因此,熟悉它们的功能十分重要

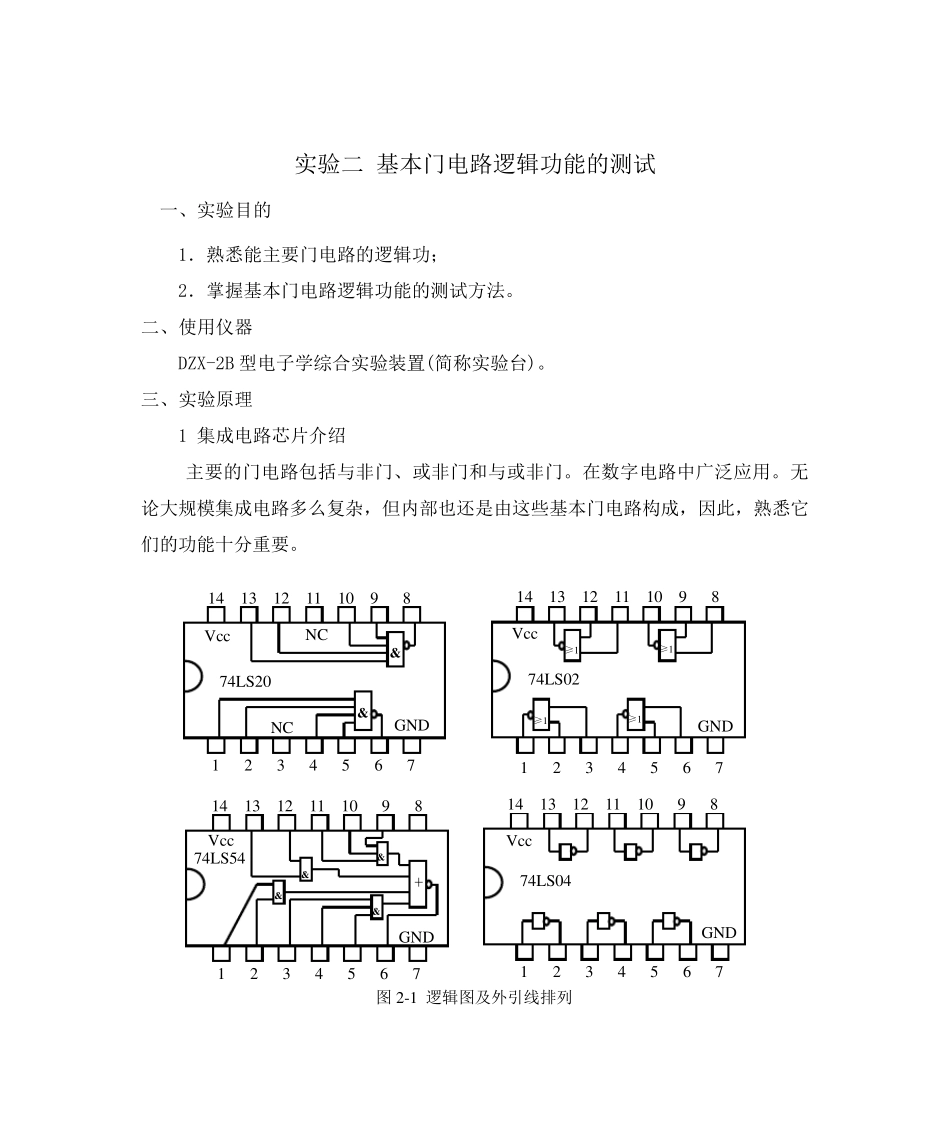

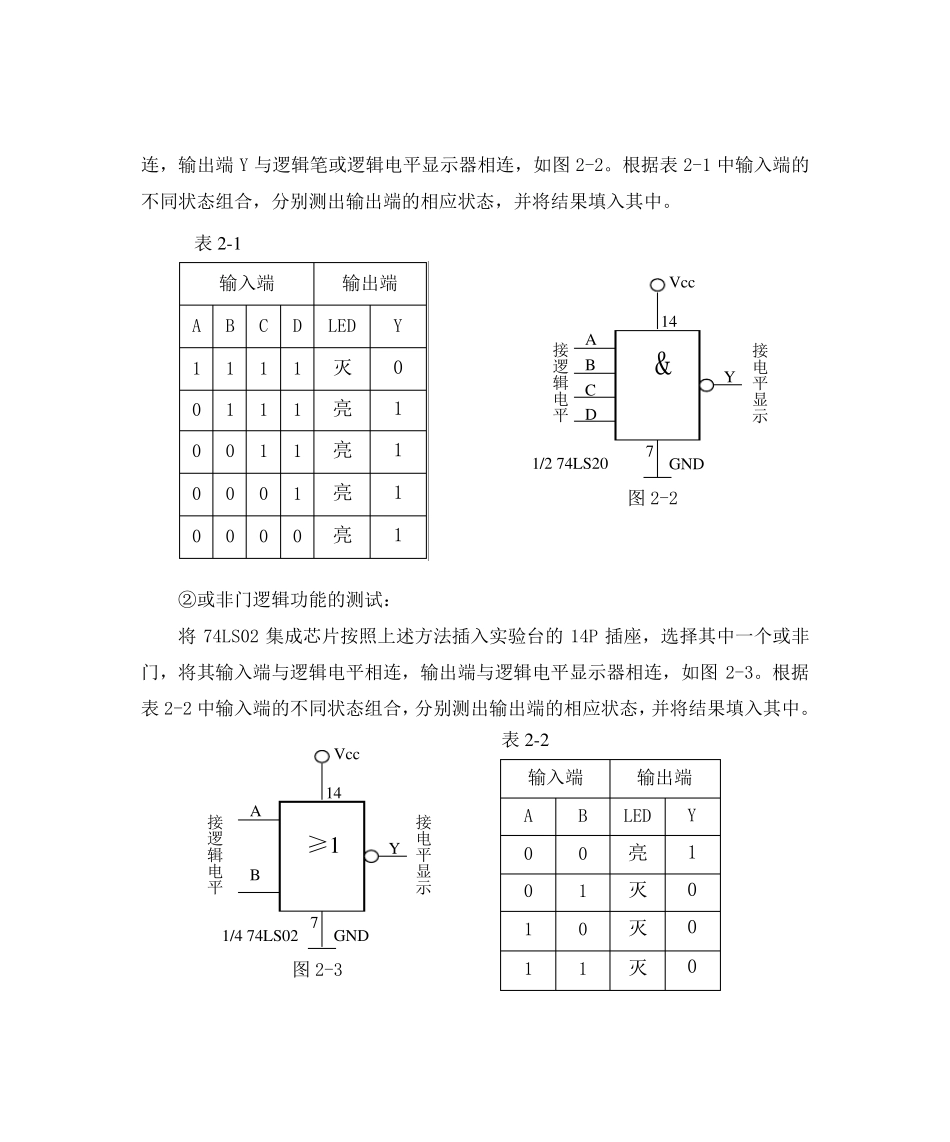

图2-1 逻辑图及外引线排列 14 13 12 11 10 9 8 1 2 3 4 5 6 7 74LS04 Vcc GND 14 13 12 11 10 9 8 1 2 3 4 5 6 7 74LS20 NC NC Vcc GND & & 14 13 12 11 10 9 8 1 2 3 4 5 6 7 74LS54 + Vcc GND & & & & 1 2 3 4 5 6 7 14 13 12 11 10 9 8 74LS02 Vcc GND ≥1 ≥1 ≥1 ≥1 数字电路实验中所用到的集成芯片多为双列直插式,其引脚排列规则如图2-1

其识别方法是:正对集成电路型号或看标记(左边的缺口或小圆点标记),从左下角开始按逆时针方向以1,2,3…依次排列到最后一脚

在标准形TTL 集成电路中,电源端Vcc 一般排在左上端,接地端(GND)一般排在右下端,如74LS00

若集成芯片引脚上的功能标号为NC,则表示该引脚为空脚,与内部电路不连接

本实验采用的芯片是74LS00 二输入四与非门、74LS20 四输入二与非门、74LS02 二输入四或非门、74LS04 六非门、74LS54 双二双三输入与或非门,逻辑图及外引线排列图见图2-1(74LS00 见实验一中图1-1(d))

逻辑表达式: 非门 AY 2-1 2 输入端与非门 BAY• 2-2 4 输入端与非门 DCBAY••• 2-3