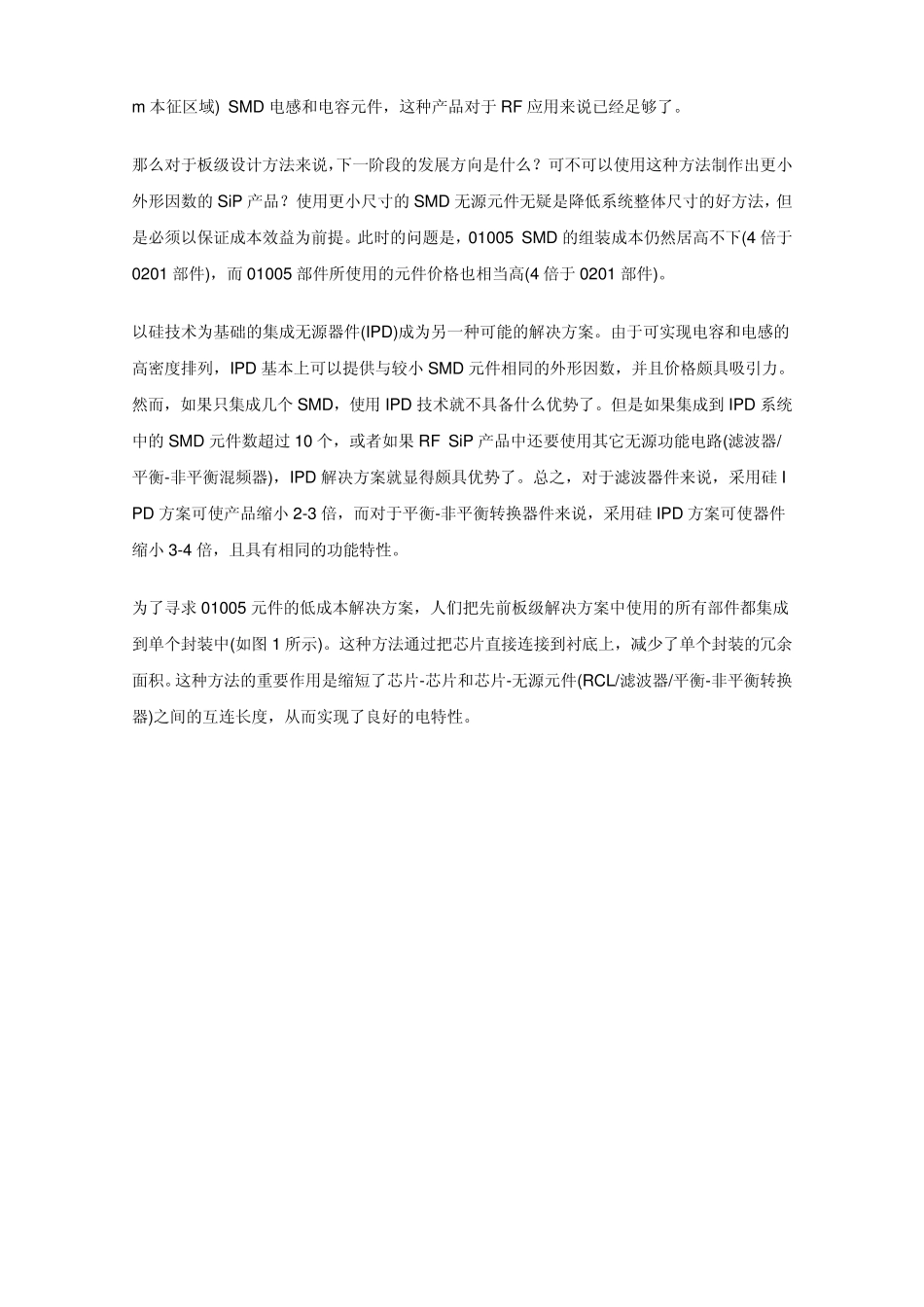

射频封装系统 0 出自:Kai Liu、Roger Emigh、Eric Gongora 和 Adam Moya,STATS ChipPAC RF 系统(如蜂窝电话)中通常包含多个集成电路 (如基带 ASIC,即 BBIC 以及 RFIC 收发机等),同时还包括大量电感、电容及电阻。以前单个 IC 是以单芯片的形式进行封装的,而 RCL(电阻电容电感)元件都是分立的,采用表面安装器件(SMD)的形式进行封装,然后把所有这些部件组装在 PCB 或小型电路板上。如果所要求的投放市场的时间较短,这种方法会有一定的优势。此外,由于组装前可以对各单个部件(IC 或 SMD 元件)进行测试,我们对板级组装产品能够实现正常功能具有足够的信心。另外,在 RF 系统中,各类元件采用不同的技术制作而成,例如 BBIC 采用 CMOS 技术、收发机采用 SiGe 和 BiCMOS 技术、RF 开关采用 GaAs 技术等。系统芯片(SOC)的优势是把所有功能整合在同一块芯片上,但却受到各种 IC 技术的限制,因此不能有效利用上述各项技术的优势。系统级封装 (SiP)可以对各种不同技术的不同电、热和机械性能要求进行权衡,最终获得最佳的性能。 引言 由于成本和性能方面的原因,在管芯中使用大量电感和电容是不实际的。使用片外 SMD 电感通常能够获得更好的 Q 因数,并且片外 SMD 电感覆盖了较宽的电感范围,与典型要求相匹配。由于大去耦电容所占面积过大,把它制作在管芯里将增加成本压力。我们制作出一种有效的 RF 系统/子系统,并证实把一定量的无源元件按照 SMD 形式进行封装的方法在未来几年中仍是最具吸引力的方法。 板级封装方法已在业界广泛应用,还有一种发展趋势是把整体 RF 系统制作在很小的外形尺寸中。IC 尺寸的缩小在技术方面严格遵守摩尔定律(每 18 个月尺寸缩小一半)的发展规律,但在经济方面,为使 IC 尺寸不断减小,却把大量资金投入到新型 IC 产品的设计和制作中。此外,芯片尺寸的下降对系统面积来说并不十分重要,因为通常情况下,大多数 SiP 产品中的有源器件(IC 封装)都不会在电路板中占据过多的面积。 在典型的 RF 设计中,60%-70%的系统面积都被无源元件(如 RCL、滤波器、平衡-非平衡混频器)所占据。为了降低产品的整体尺寸,迫切需要缩小这些无源元件的尺寸。在过去的几年中,SMD 电感和电容的密度得到了明显改进。目前市场上购买的大都是 01005(250μm×125μm本征区域) SMD 电感和电容元件,这种产品对于RF 应用来说已经足够了。 那么对于板级设计方...