英特尔为什么牛逼——后栅极工艺浅谈(一)Jeff_Hill|2013-11-1317:14|阅读:2584|评论:39半导体制程工艺上,英特尔要是说第二,那没人敢说第一

晶圆制造这个圈子,英特尔毫无疑问处于第一流,其他厂商包括 IBM,英飞凌,NEC,意法半导体以及东芝等公司,以及目前半导体代工行业的老大老二老三——台积电、GlobalFoundries、三星,统统都是二流

说这么绝对可能有人不服,小编举最近的一个例子,英特尔仅仅破一次例为美国芯片制造商 Altera 代工首个四核 64 位 ARMCortex-A53 处理器,就引发了业界一片惊叹

为了让大家一窥 Intel 在半导体制造工艺上的牛逼,笔者选取数月前参加 Intel 新品交流会后,印象深刻的 45nm 以下 HKMG 的成型工艺来做探讨

随着晶体管尺寸的不断缩小,HKMG(high-k 绝缘层+金属栅极)技术几乎已经成为45nm 以下级别制程的必备技术

不过在制作 HKMG 结构晶体管的工艺方面,业内却存在两大各自固执己见的不同阵营,以 IBM 为代表的前栅极 Gate-first 工艺流派和以 Intel 为代表的后栅极 GateTast 工艺流派

更准确点说,在步入 HKMG 时代之初,只有 Intel 和其他所有半导体企业之别

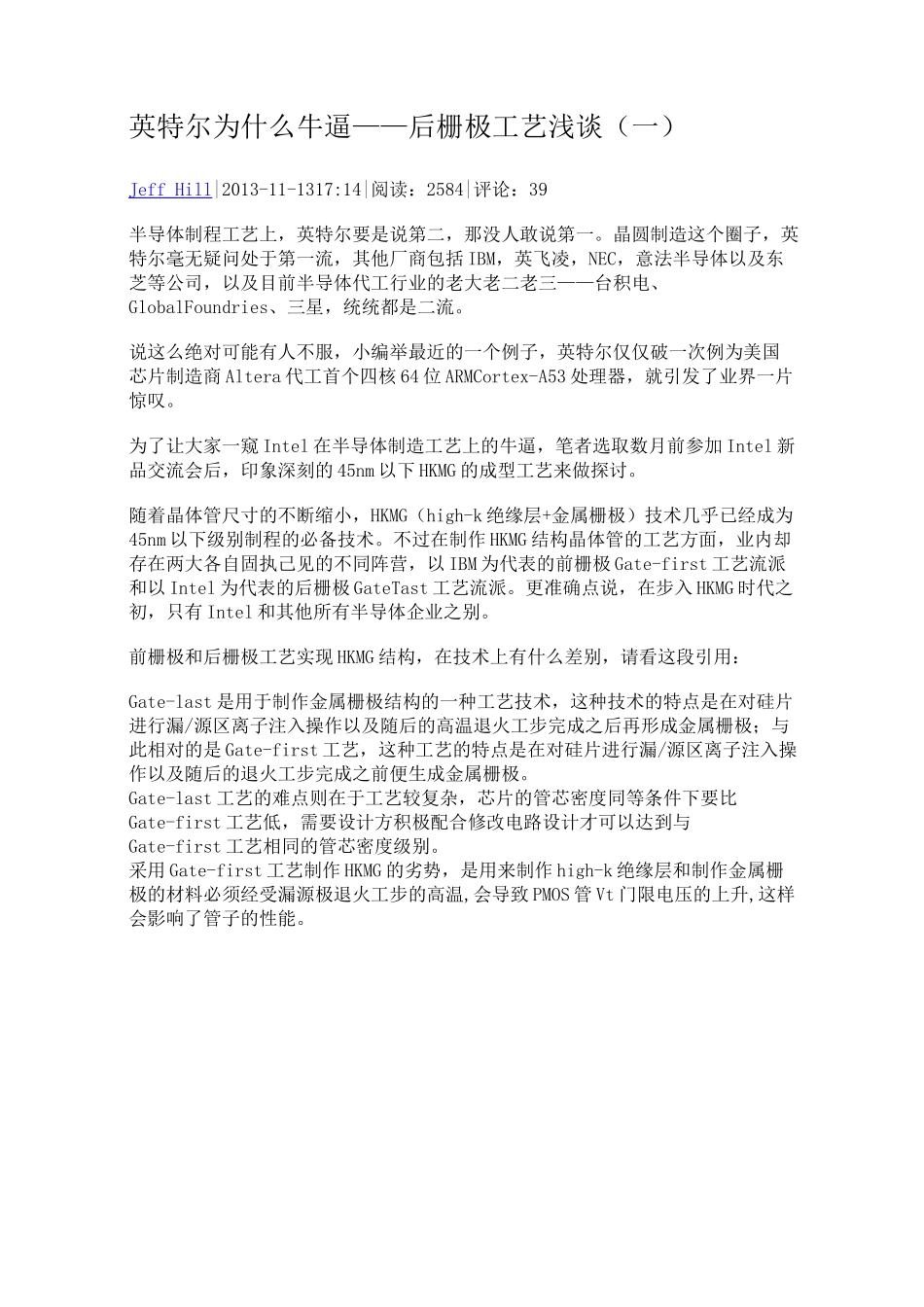

前栅极和后栅极工艺实现 HKMG 结构,在技术上有什么差别,请看这段引用:Gate-last 是用于制作金属栅极结构的一种工艺技术,这种技术的特点是在对硅片进行漏/源区离子注入操作以及随后的高温退火工步完成之后再形成金属栅极;与此相对的是 Gate-first 工艺,这种工艺的特点是在对硅片进行漏/源区离子注入操作以及随后的退火工步完成之前便生成金属栅极

Gate-last 工艺的难点则在于工艺较复杂,芯片的管芯密度同等条件下要比Gate-first 工艺低,需要设计方积极配合