用SpectreVerilog 进行模数混仿,以Sigma-Delta ADC 为例 loghere loghere@126

com SpectreVerilog 模数混仿, 模拟部分用Spectre, 数字部分用Verilog-XL

所以还需要安装 Cadence LDV 软件, 其内含Verilog-XL 仿真器

这里以自行设计的二阶全差分Sigma-Delta ADC 为例, 详细介绍用SpectreVerilog 的仿真过 程

所用工艺库为TSMC 0

18u ,电源电压:1

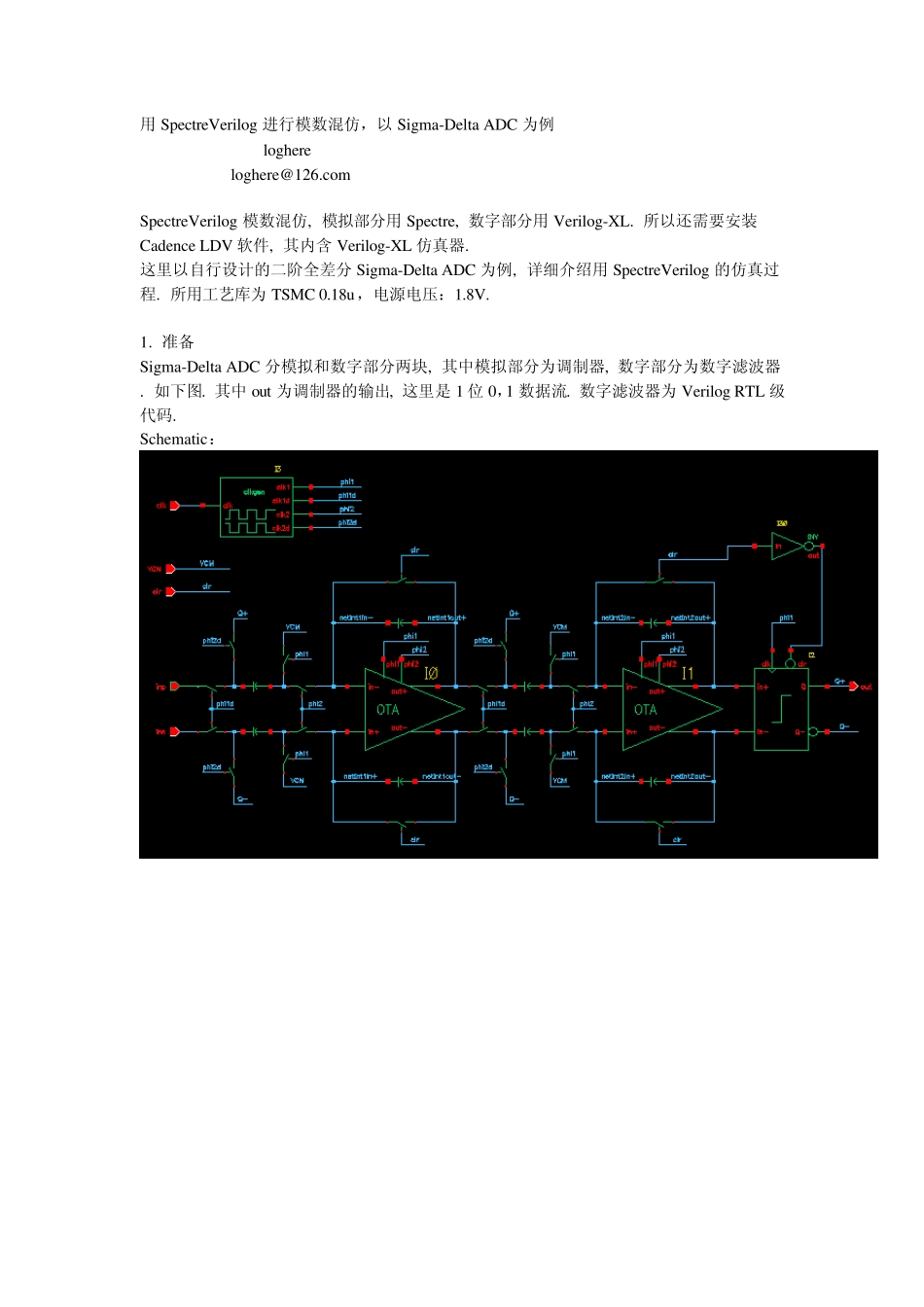

准备 Sigma-Delta ADC 分模拟和数字部分两块, 其中模拟部分为调制器, 数字部分为数字滤波器

其中ou t 为调制器的输出, 这里是 1 位 0,1 数据流

数字滤波器为Verilog RTL 级 代码

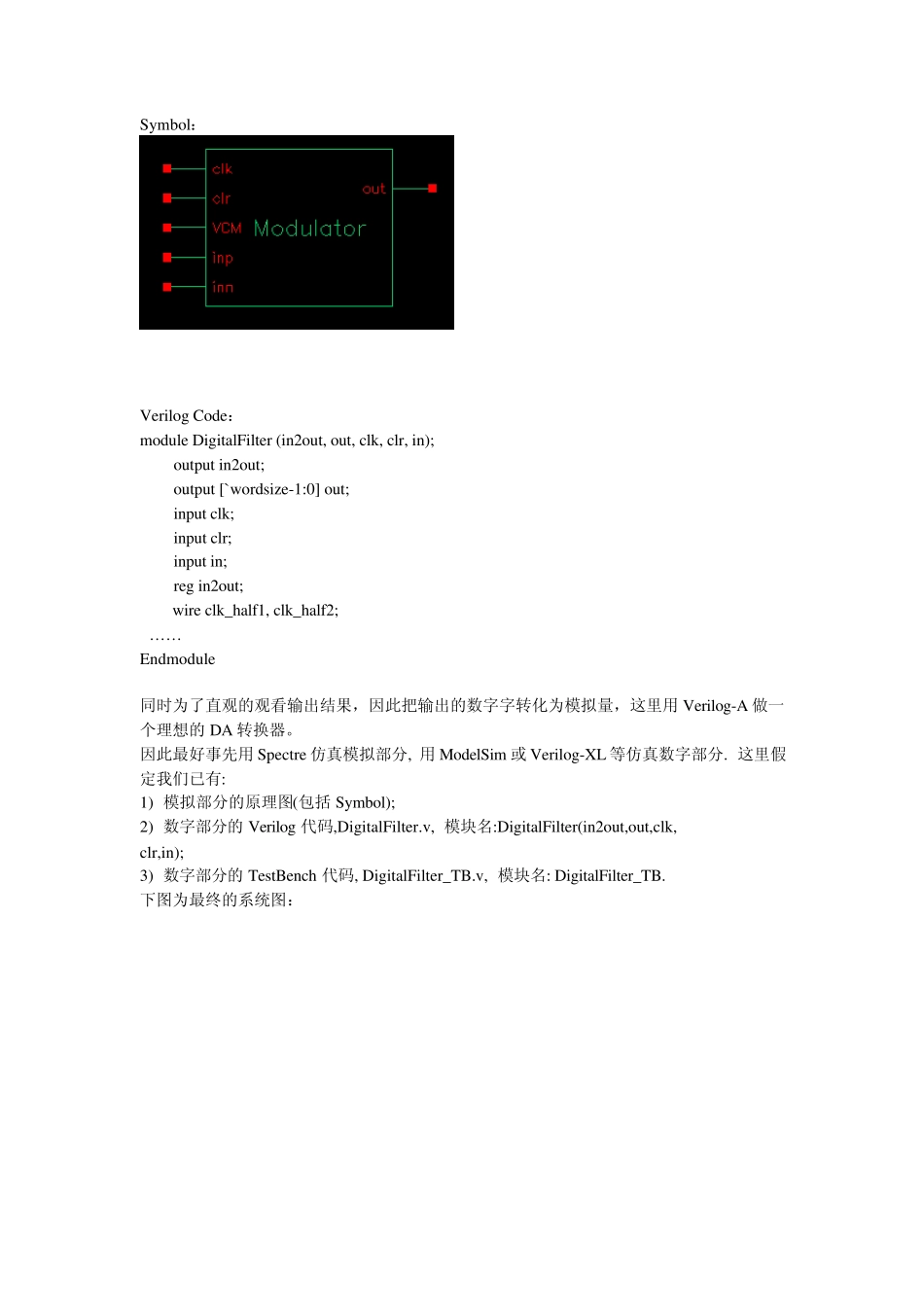

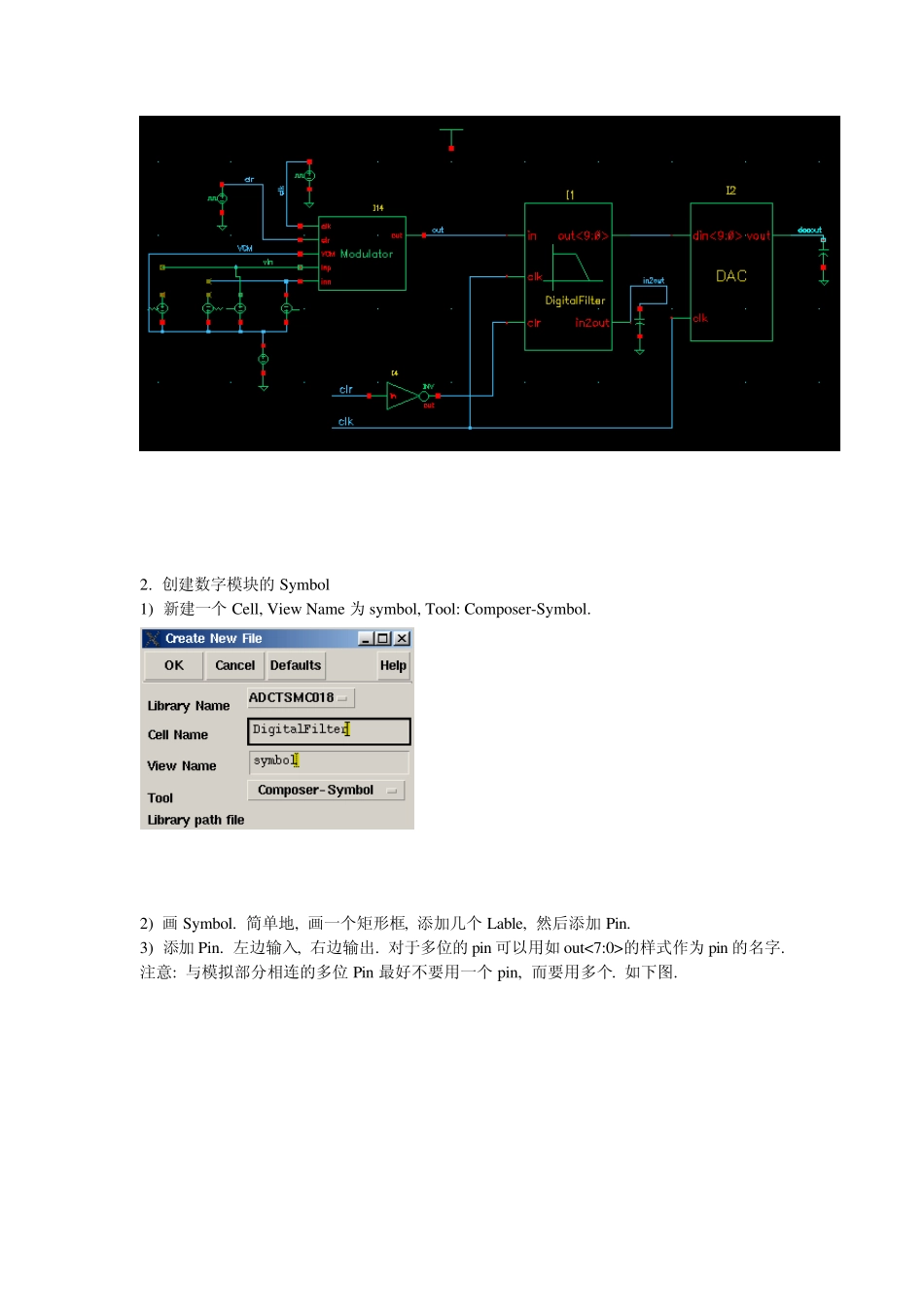

Schematic: Symbol: Verilog Code: module DigitalFilter (in2out, out, clk, clr, in); output in2out; output [`wordsize-1:0] out; input clk; input clr; input in; reg in2out; wire clk_half1, clk_half2; …… Endmodule 同时为了直观的观看输出结果,因此把输出的数字字转化为模拟量,这里用Verilog-A 做一 个理想的DA 转换器

因此最好事先用Spectre 仿真模拟部分, 用ModelSim 或 Verilog-XL 等仿真数字部分

这里假 定我们已有: 1) 模拟部分的原理图(包括 Symbol); 2) 数字部分的Verilog 代码,DigitalFilter

v, 模块名:DigitalFilter(in2out,out,clk,