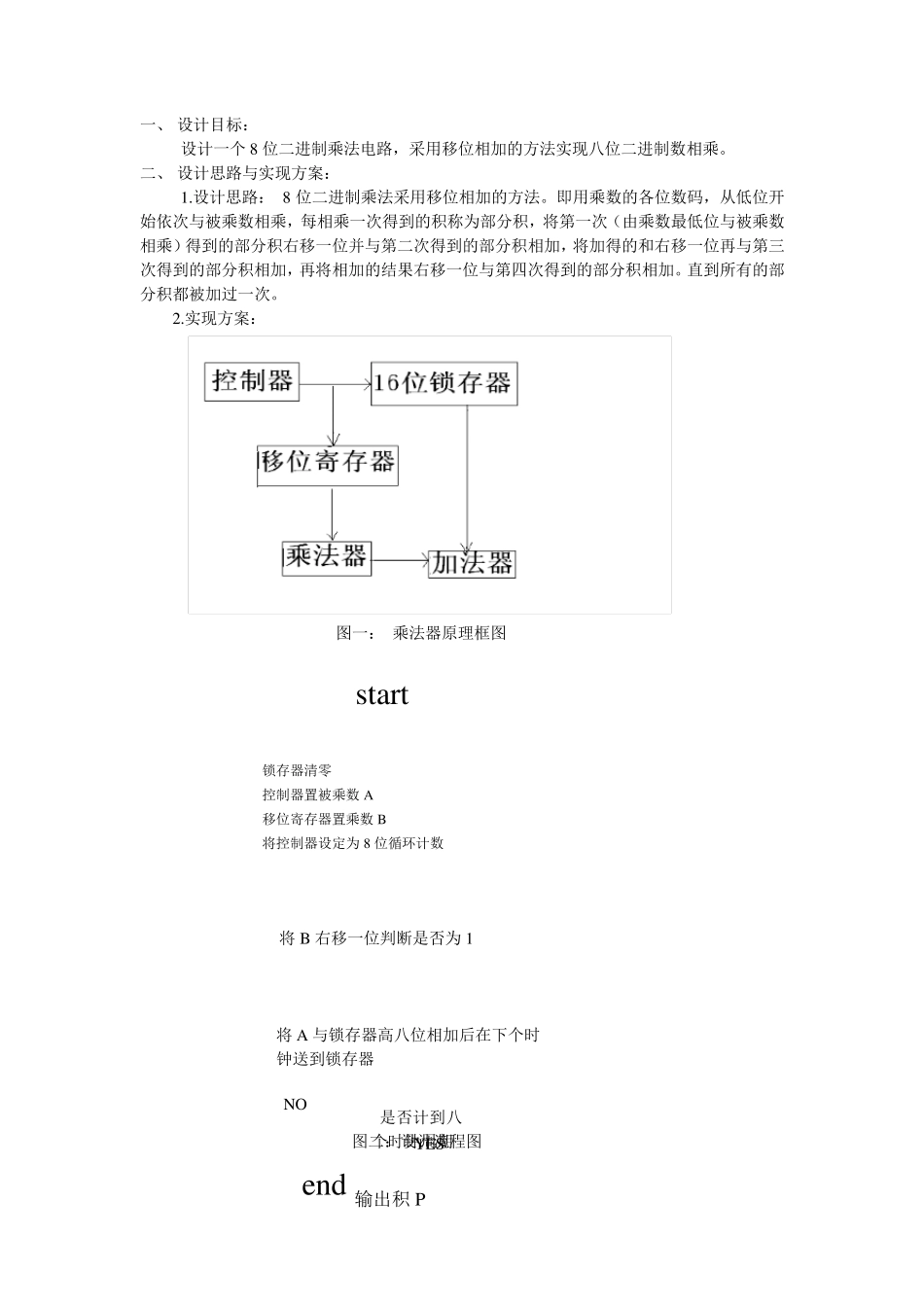

一、 设计目标: 设计一个 8 位二进制乘法电路,采用移位相加的方法实现八位二进制数相乘。 二、 设计思路与实现方案: 1.设计思路: 8 位二进制乘法采用移位相加的方法。即用乘数的各位数码,从低位开始依次与被乘数相乘,每相乘一次得到的积称为部分积,将第一次(由乘数最低位与被乘数相乘)得到的部分积右移一位并与第二次得到的部分积相加,将加得的和右移一位再与第三次得到的部分积相加,再将相加的结果右移一位与第四次得到的部分积相加。直到所有的部分积都被加过一次。 2.实现方案: 图一: 乘法器原理框图 图二:设计流程图 start 锁存器清零 控制器置被乘数 A 移位寄存器置乘数 B 将控制器设定为 8 位循环计数 将 B 右移一位判断是否为 1 将 A 与锁存器高八位相加后在下个时钟送到锁存器 end 输出积 P 是否计到八个时钟周期 YES NO 三、设计过程: 模块一:8 位右移寄存器: 源程序:library ieee; use ieee.std_logic_1164.all; entity sreg8b is port(clk:IN STD_LOGIC; LOAD:IN STD_LOGIC; din:IN STD_LOGIC_VECTOR(7 DOWNTO 0); qb:out std_logic); end sreg8b; architecture behave of sreg8b is signal reg8:std_logic_vector(7 downto 0); begin process(clk,load) begin if load='1'then reg8<=din; elsif clk'event and clk='1'then reg8(6 downto 0 )<=reg8(7 downto 1); end if; end process; qb<=reg8(0); end behave; 仿真波形: 每个时钟周期将输入右移一位输出。 图三:8 位右移寄存器仿真结果 模块二:8 位加法器: 源程序:library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity adder8 is port(b,a:in std_logic_vector(7 downto 0); s:out std_logic_vector(8 downto 0)); end adder8; architecture behave of adder8 is begin s<='0'&a+b; end behave; 仿真波形: 图四: 8 位加法器仿真结果 模块三、16 位锁存器源程序 源程序:library ieee; use ieee.std_logic_1164.all; entity reg16b is port(clk,clr:in std_logic; d:in std_logic_vector(8 downto 0); q:out std_logic_vector(15 downto 0); as:out std_logic_vector(7 downto 0));end reg16b; architecture behave of reg16b is signal r16s:std_logic...