DDPP 课程设计八位 LED 可控移位显示设计与实现本设计基于 Xilinx ISE Design Suite 13

2 软件开发平台和其综合工具进行八位 LED 可控移位显示数字电路的功能设计,在 FPGA BSSYS2 开发板上来完成设计的测试和实现

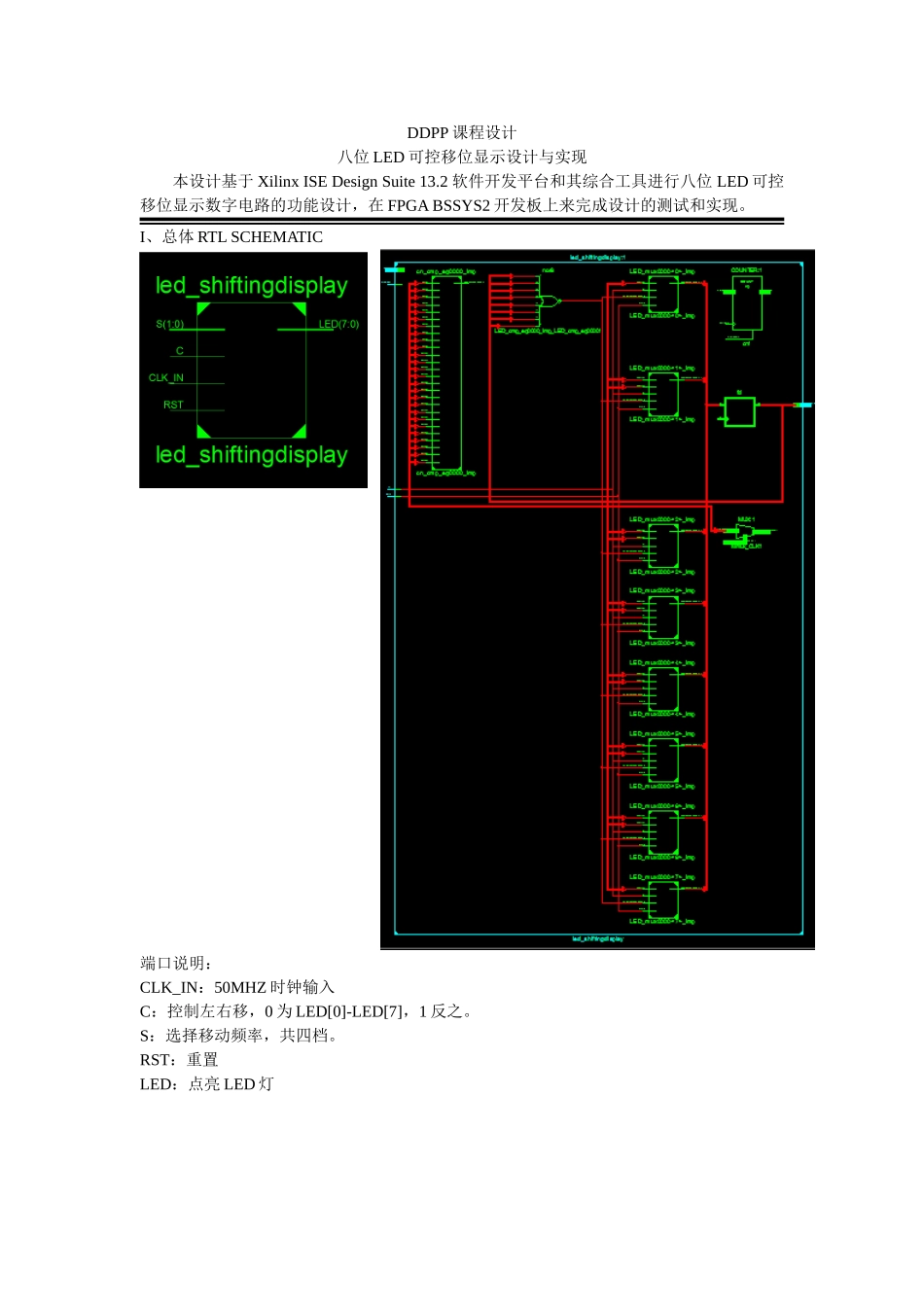

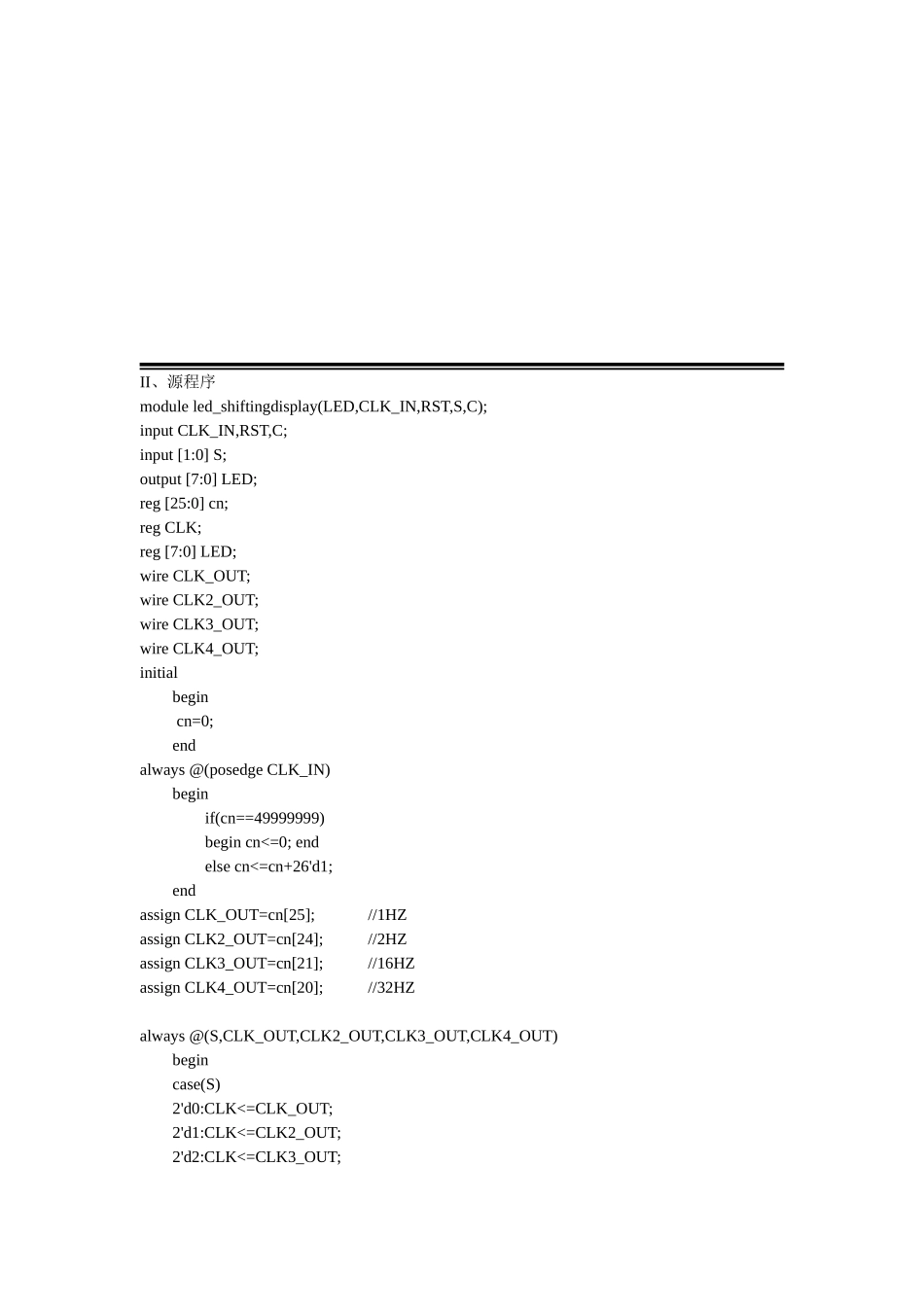

I、总体 RTL SCHEMATIC端口说明:CLK_IN:50MHZ 时钟输入C:控制左右移,0 为 LED[0]-LED[7],1 反之

S:选择移动频率,共四档

RST:重置LED:点亮 LED 灯II、源程序module led_shiftingdisplay(LED,CLK_IN,RST,S,C);input CLK_IN,RST,C;input [1:0] S;output [7:0] LED;reg [25:0] cn;reg CLK;reg [7:0] LED;wire CLK_OUT;wire CLK2_OUT;wire CLK3_OUT;wire CLK4_OUT;initial begin cn=0;endalways @(posedge CLK_IN)beginif(cn==49999999)begin cn