具有 Avalon 接口的通用异步收发器( universal asynchronous receiver/transmitter——UART) 内核实现了Altera FPGA 片上的嵌入式系统和片外设备之间的串行的字符流传输的一种方法

UART 内核实现了RS-232 协议的定时,并且提供可调的波特率,奇偶校验位、停止和数据位,以及可选的RTS/CTS 流控制信号

特性集是可配置的,允许设计者只实现特定系统的必要的功能

UART 内核提供了寄存器映射的Avalon 从接口,这样就允许Avalon 主外设(如 Nios II 处理器)通过读/写数据和控制寄 存器和UART 内核通信

UART 内核在 SOPC Builder 中提供,并且可以很容易地集成到任意的SOPC Builder生成的系统中

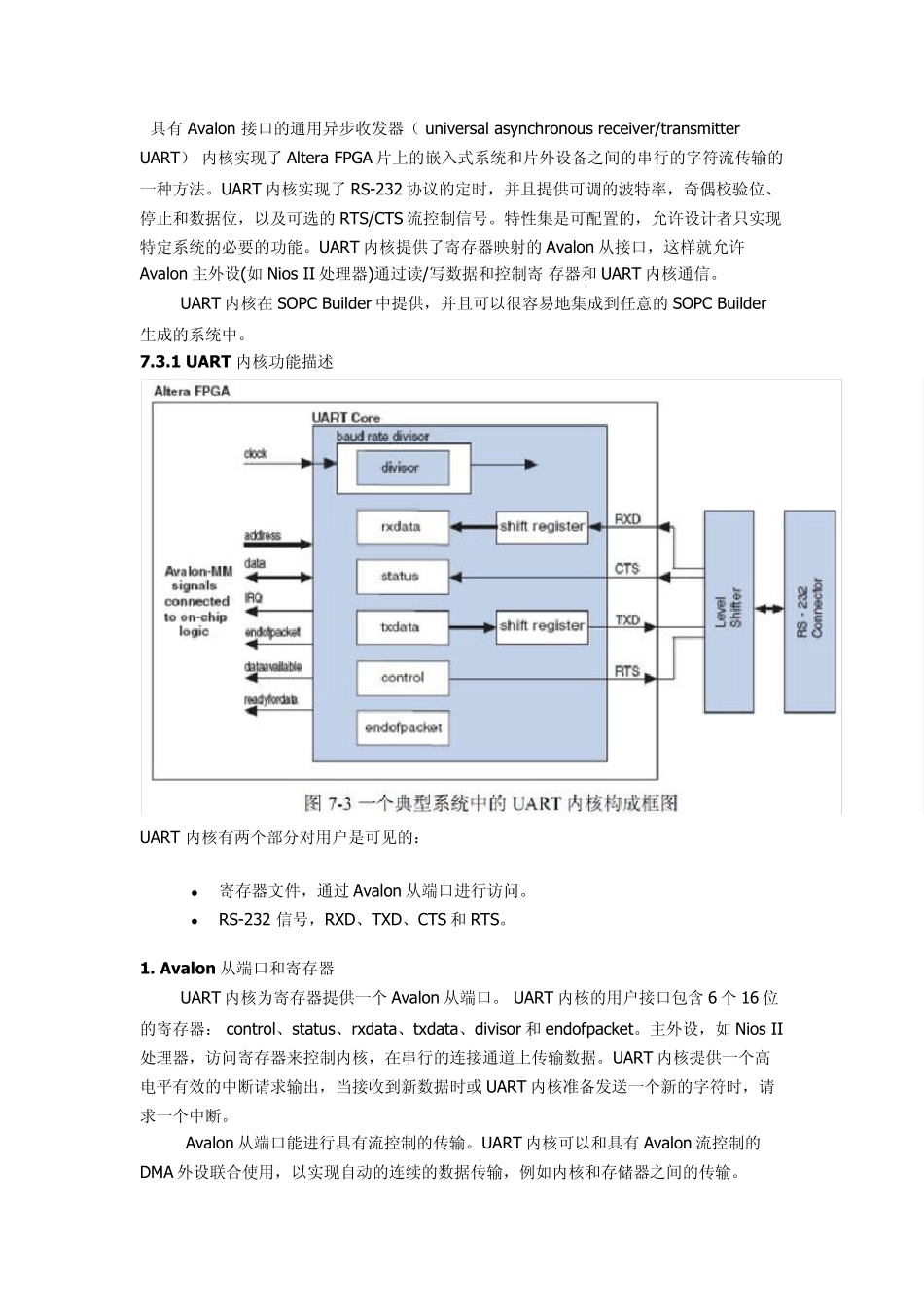

1 UART 内核功能描述 UART 内核有两个部分对用户是可见的: 寄存器文件,通过 Avalon 从端口进行访问

RS-232 信号,RXD、TXD、CTS 和RTS

Avalon 从端口和寄存器 UART 内核为寄存器提供一个 Avalon 从端口

UART 内核的用户接口包含 6 个 16 位的寄存器: control、status、rxdata、txdata、divisor 和endofpacket

主外设,如 Nios II处理器,访问寄存器来控制内核,在串行的连接通道上传输数据

UART 内核提供一个高电平有效的中断请求输出,当接收到新数据时或 UART 内核准备发送一个新的字符时,请求一个中断

Avalon 从端口能进行具有流控制的传输

UART 内核可以和具有Avalon 流控制的DMA 外设联合使用,以实现自动的连续的数据传输,例如内核和存储器之间的传输

RS-232 接口 UART 内核实现RS-232 异步发送和