第九章 DDR 存贮器控制器 9

1 绪论 完全可编程的DDR SDRAM 控制器支持大多数第一代JEDEC 标准的、可用的x8 或x16 DDR和DDR2 存贮器,包括非缓存式和寄存式DIMM,但不支持在同一个系统中混合使用不同的存贮器类型或非缓存式和寄存式DIMM

内置的错误检测和校正(ECC)保证可靠的高频操作具有极低的位差错率

动态电源管理和自动预充电模式简化了存贮器系统的设计

丰富的特有特性,包括ECC差错注入,支持快速系统调试

注意 本章中,“存贮体(bank)”指由一个片选指定的实际存贮体;“逻辑存贮体(logical bank)”指每个SDRAM 芯片中四个或八个子存贮体中的一个

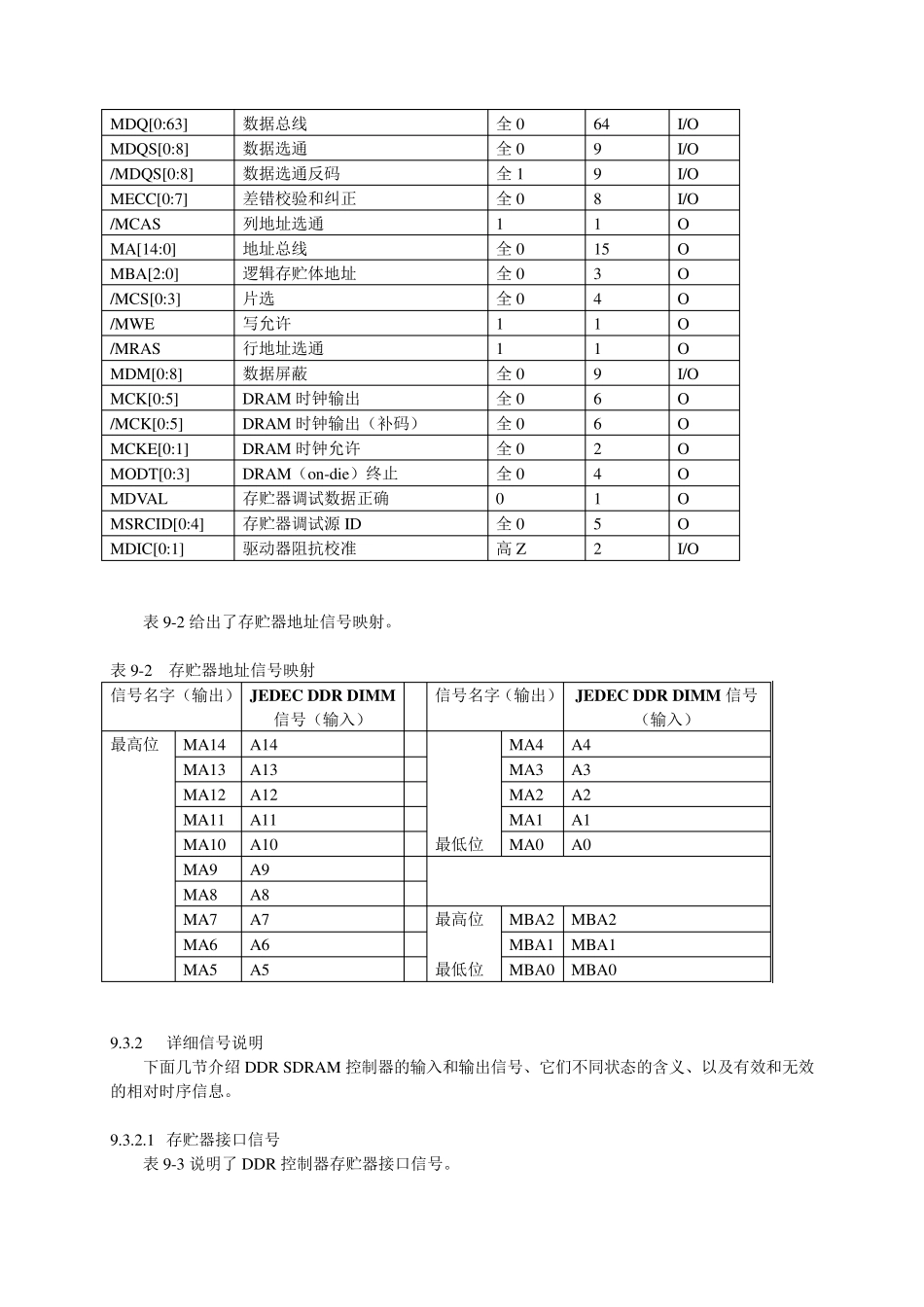

一个子存贮体由存贮器访问期间存贮体地址(MBA)上的两位或三位指定

图 9-1 是 DDR 存贮器控制器及其相关接口的概要结构图

5 节“功能描述”包括该控制器的详图

图 9-1 DDR 存贮器控制器简化结构图 9

2 特性 DDR 存贮器控制器包括这些与众不同的特性: 支持DDR 和DDR2 SDRAM 64/72 位SDRAM 数据总线

支持DDR 和DDR2 的32/40 位SDRAM 数据总线 满足所有SDRAM 定时参数的可编程设置 支持下列SDRAM 配置: 四个物理存贮体(片选),每个存贮体独立寻址 带有x8/x16/x32 数据端口的64M 位到4G 位设备(无直接x4 支持) 非缓存式和寄存式DIMM 芯片选择交叉支持 支持数据屏蔽信号和子双字(sub-double-word)写的读-修改-写

注意,仅在 ECC 启用时,读-修改-写才是必要的

支持两位差错检测和一位差错恢复 ECC(8 位校验字校验 64 位数据) 四表项输入请求队列 打开页面管理(每个逻辑存贮体都有专门的表项) 自动 DRAM 初