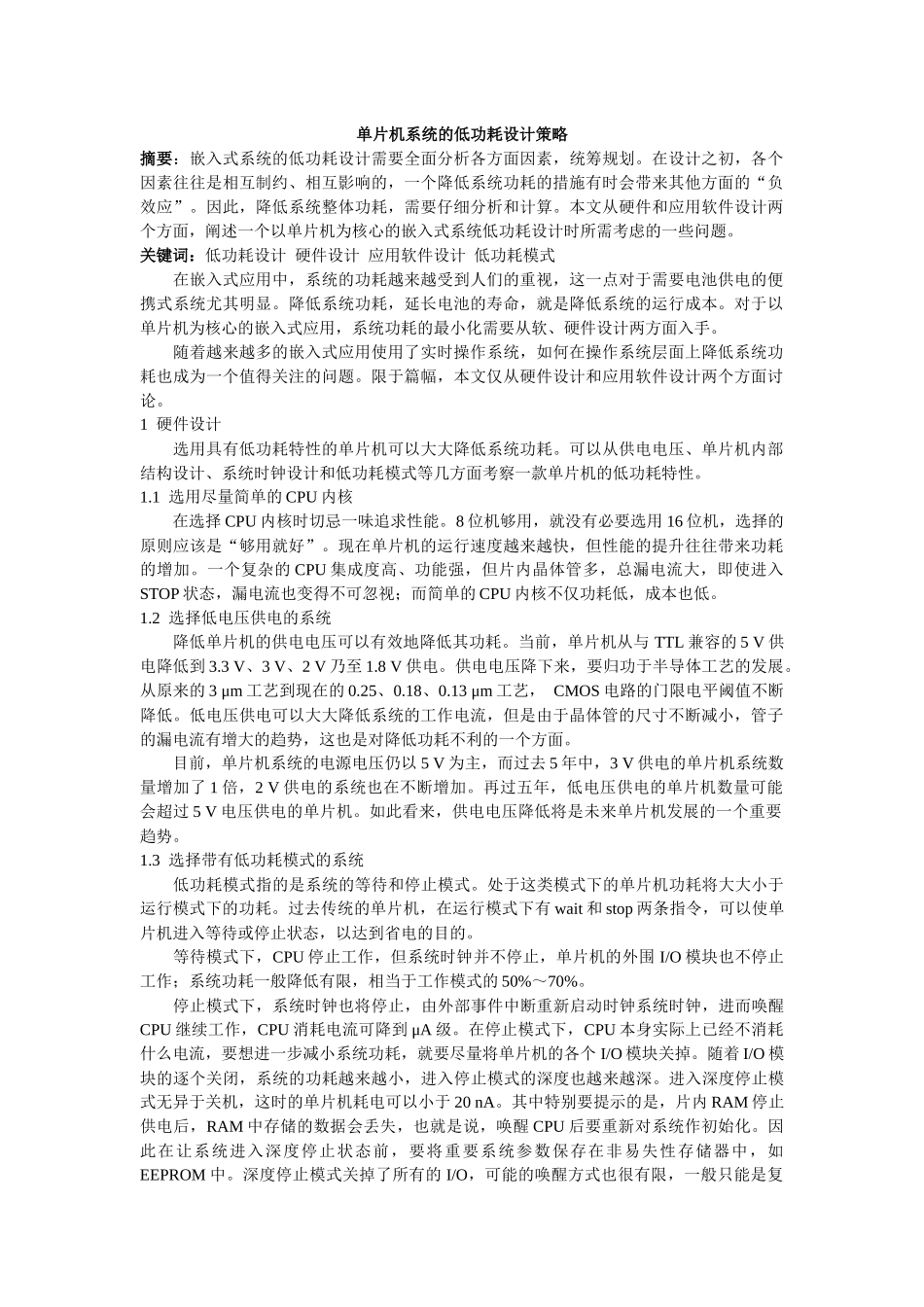

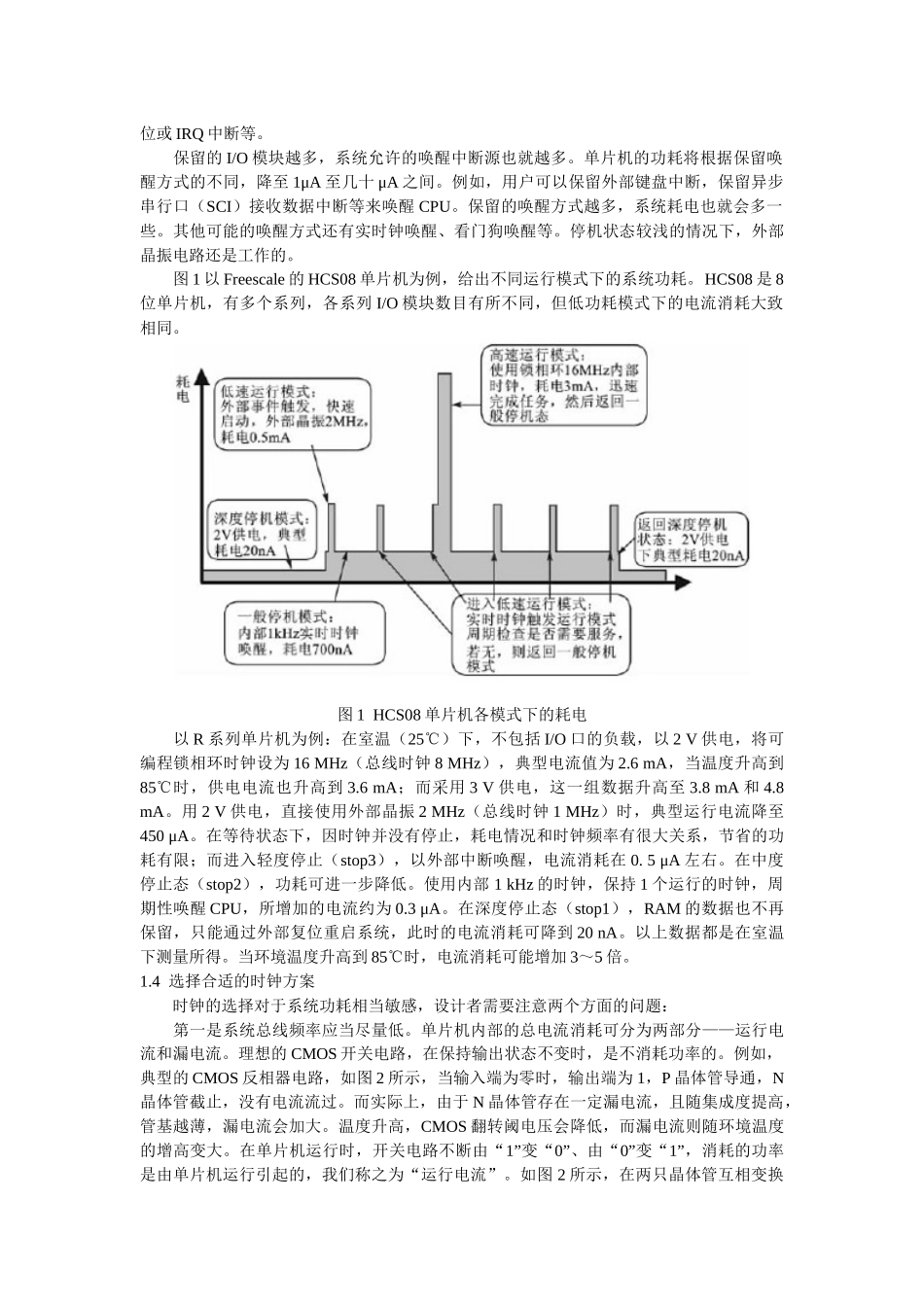

单片机系统的低功耗设计策略摘要:嵌入式系统的低功耗设计需要全面分析各方面因素,统筹规划。在设计之初,各个因素往往是相互制约、相互影响的,一个降低系统功耗的措施有时会带来其他方面的“负效应”。因此,降低系统整体功耗,需要仔细分析和计算。本文从硬件和应用软件设计两个方面,阐述一个以单片机为核心的嵌入式系统低功耗设计时所需考虑的一些问题。关键词:低功耗设计 硬件设计 应用软件设计 低功耗模式 在嵌入式应用中,系统的功耗越来越受到人们的重视,这一点对于需要电池供电的便携式系统尤其明显。降低系统功耗,延长电池的寿命,就是降低系统的运行成本。对于以单片机为核心的嵌入式应用,系统功耗的最小化需要从软、硬件设计两方面入手。 随着越来越多的嵌入式应用使用了实时操作系统,如何在操作系统层面上降低系统功耗也成为一个值得关注的问题。限于篇幅,本文仅从硬件设计和应用软件设计两个方面讨论。1 硬件设计 选用具有低功耗特性的单片机可以大大降低系统功耗。可以从供电电压、单片机内部结构设计、系统时钟设计和低功耗模式等几方面考察一款单片机的低功耗特性。1.1 选用尽量简单的 CPU 内核 在选择 CPU 内核时切忌一味追求性能。8 位机够用,就没有必要选用 16 位机,选择的原则应该是“够用就好”。现在单片机的运行速度越来越快,但性能的提升往往带来功耗的增加。一个复杂的 CPU 集成度高、功能强,但片内晶体管多,总漏电流大,即使进入STOP 状态,漏电流也变得不可忽视;而简单的 CPU 内核不仅功耗低,成本也低。1.2 选择低电压供电的系统 降低单片机的供电电压可以有效地降低其功耗。当前,单片机从与 TTL 兼容的 5 V 供电降低到 3.3 V、3 V、2 V 乃至 1.8 V 供电。供电电压降下来,要归功于半导体工艺的发展。从原来的 3 μm 工艺到现在的 0.25、0.18、0.13 μm 工艺, CMOS 电路的门限电平阈值不断降低。低电压供电可以大大降低系统的工作电流,但是由于晶体管的尺寸不断减小,管子的漏电流有增大的趋势,这也是对降低功耗不利的一个方面。 目前,单片机系统的电源电压仍以 5 V 为主,而过去 5 年中,3 V 供电的单片机系统数量增加了 1 倍,2 V 供电的系统也在不断增加。再过五年,低电压供电的单片机数量可能会超过 5 V 电压供电的单片机。如此看来,供电电压降低将是未来单片机发展的一个重要趋势。1.3 选择带有低功耗模式的系统 低功耗模式...