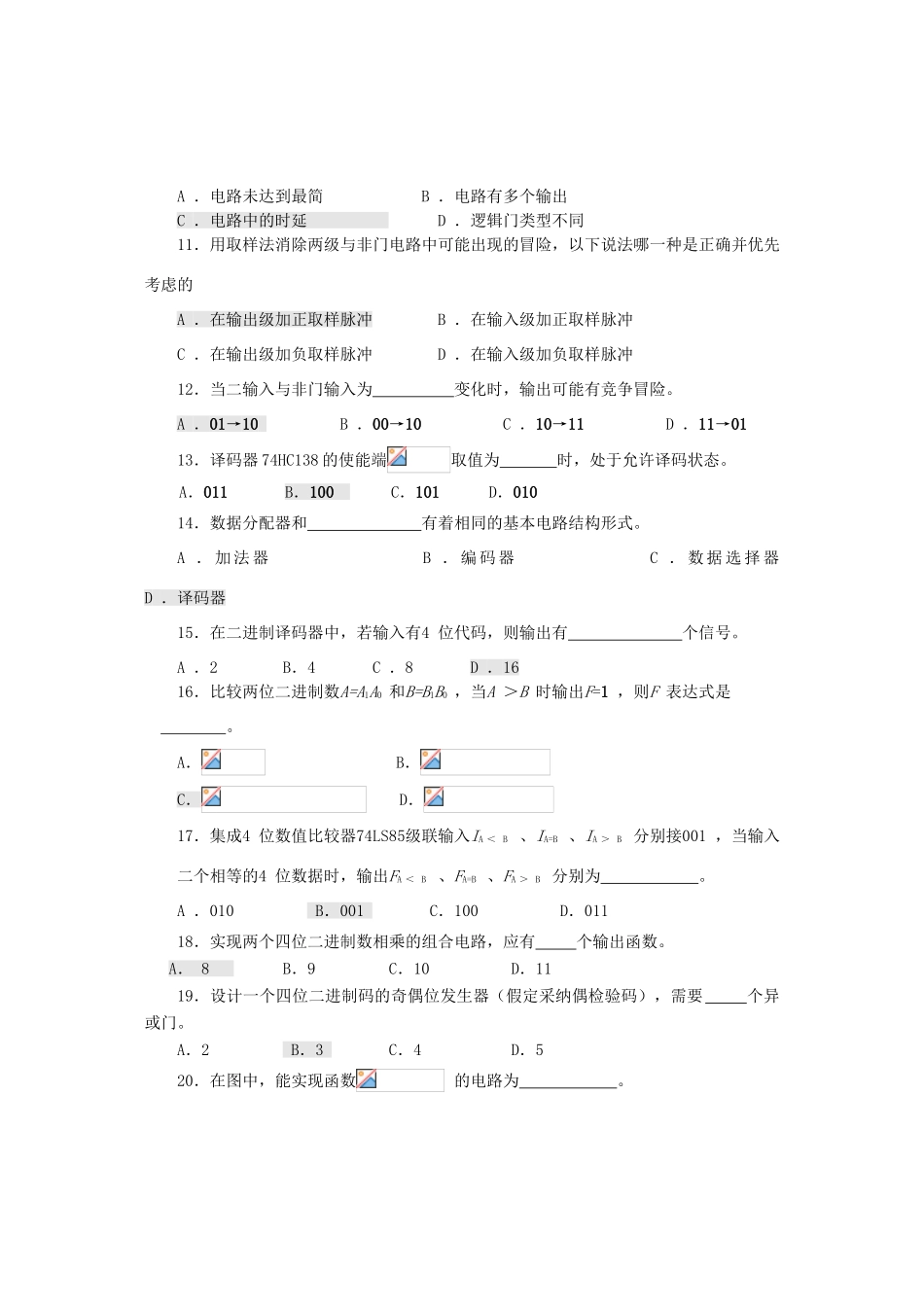

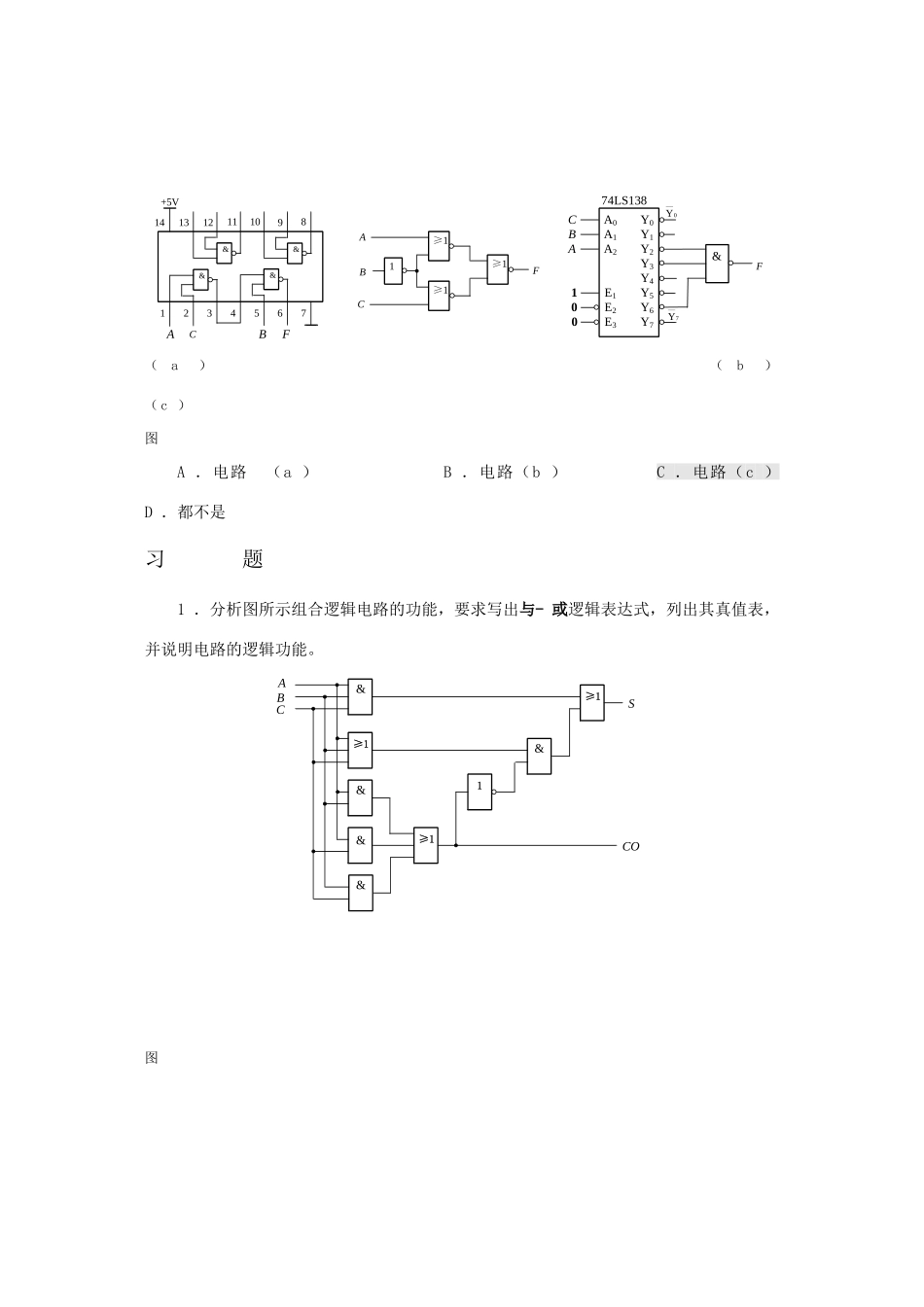

(有些题答案错了) 自 我 检 测 题1 .组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与以前的输入信号 无关 。2 .在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 竞争冒险 。3.8 线—3 线优先编码器 74LS148 的优先编码顺序是、、、…、,输出为。输入输出均为低电平有效。当输入…为时,输出为 010 。4 .3 线—8 线译码器74HC138 处于译码状态时,当输入A2A1A0=001 时,输出= 。5 .实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫 数据分配器 。6.根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。7 .一位数值比较器,输入信号为两个要比较的一位二进制数,用A 、B 表示,输出信号为比较结果:Y(A> B) 、Y(A= B) 和Y(A< B) ,则Y(A> B) 的逻辑表达式为。8 .能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。9.多位加法器采纳超前进位的目的是简化电路结构 × 。 (√,× )10.组合逻辑电路中的冒险是由于 引起的。A .电路未达到最简 B .电路有多个输出C .电路中的时延 D .逻辑门类型不同11.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的A .在输出级加正取样脉冲 B .在输入级加正取样脉冲C .在输出级加负取样脉冲 D .在输入级加负取样脉冲12.当二输入与非门输入为 变化时,输出可能有竞争冒险。A .01→10 B .00→10 C .10→11 D .11→0113.译码器 74HC138 的使能端取值为 时,处于允许译码状态。A.011 B.100 C.101 D.01014.数据分配器和 有着相同的基本电路结构形式。A . 加 法 器 B . 编 码 器 C . 数 据 选 择 器 D .译码器15.在二进制译码器中,若输入有4 位代码,则输出有 个信号。A .2 B.4 C .8 D .1616.比较两位二进制数A=A1A0 和B=B1B0 ,当A >B 时输出F=1 ,则F 表达式是 。 A. B. C. D.17.集成4 位数值比较器74LS85级联输入IA < B 、IA=B 、IA > B 分别接001 ,当输入二个相等的4 位数据时,输出FA < B 、FA=B 、FA > B 分别为 。A .010 B.001 C.100 D.01118.实现两个四位二进制数相乘的组合电路,应有 个输出函数。A. 8 B.9 C.10 D.11 19.设计一个四位二进制码的奇偶位发生器(假定采...