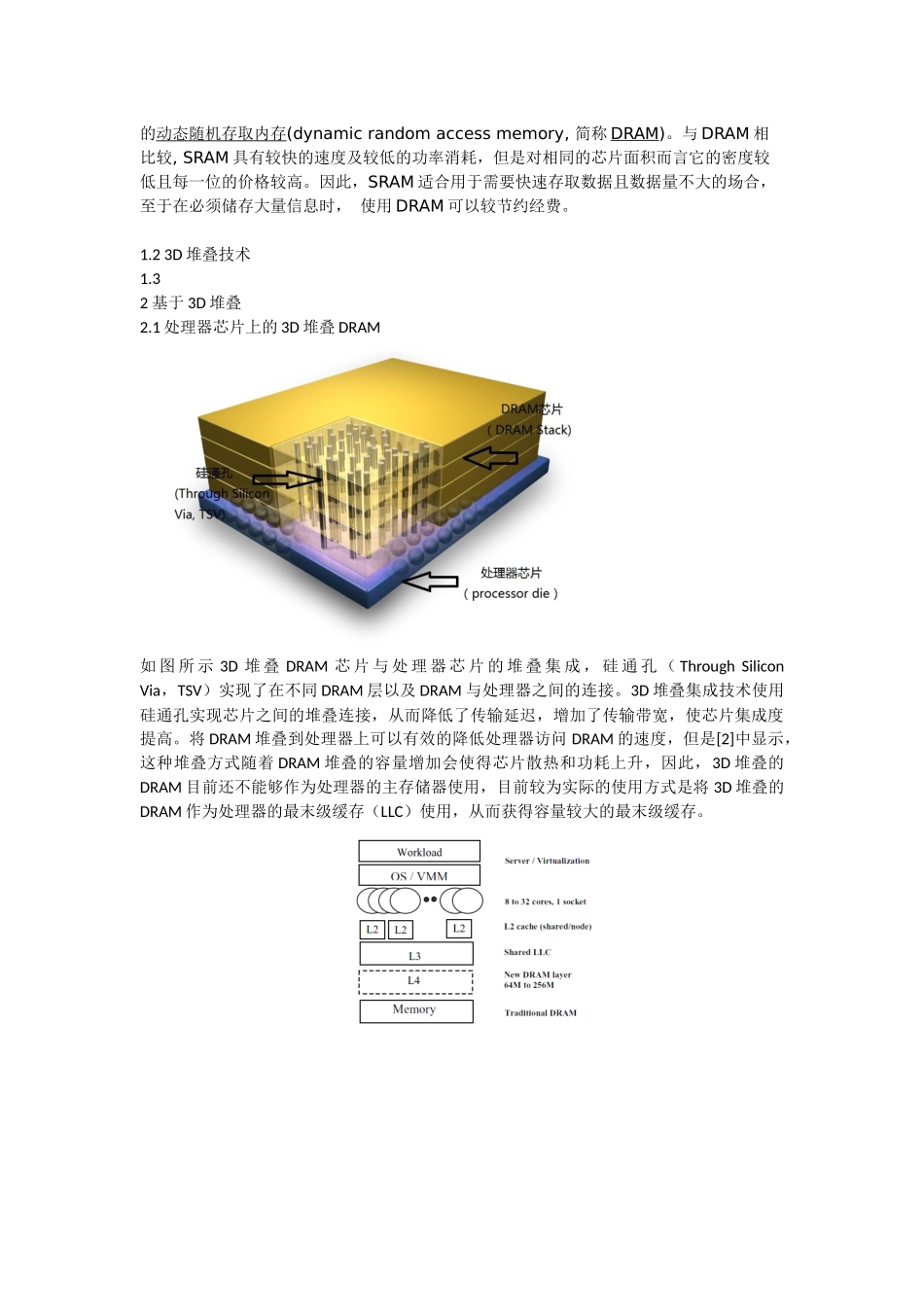

基于 3D 堆叠集成的 DRAM 缓存架构讨论综述摘要:内存访问速度的增长远远跟不上处理器处理性能的增长,“内存墙(Memory Wall)[1]”越来越成为计算机体系结构进步的瓶颈。3D 堆叠集成技术将多层硅芯片叠加起来,使得芯片间传输延迟降低,传输带宽增加。使用 3D 堆叠技术可以将 DRAM 堆叠到多核处理器芯片上,从而使得访存速度获得提高。由于散热,功耗等问题,基于 3D 堆叠集成的 DRAM 往往不具有足够的容量来作为处理器的主存(除了一些特别的市场需求)。较为有实践意义的架构是将基于 3D 堆叠集成的 DRAM 作为最末级缓存(LLC Last Level Cache)使用。本文分析了已有的基于 3D 堆叠集成的 DRAM 缓存架构,比较了不同架构之间的优缺点,对目前该领域的讨论方向做了综述。关键词:3D 堆叠;DRAM;缓存1 引言1.1 内存墙及现代存储技术1965 年,Intel 的创始人之一,名誉主席戈登.摩尔(Gordon Moore)提出:每 18 个月,芯片上的晶体管数目就能够增加一倍。这就是著名的摩尔定律。摩尔定律的另一个更为大家熟悉的表述是:每 18 个月,CPU 的速度提高一倍。过去 40 年,通用 CPU 的速度基本按这个预测在进展。现在 CPU 的速度超过 2.8GHz,实际上还可以做到更高。但是,CPU 速度的提高并不意味着 CPU 的实际性能也有相应的提高。在过去 40 年中,CPU 核心的速度提高了近千倍,但是内存的速度提高却不大;更为关键的是,内存的延迟没有降低。这使得内存延迟已经成为了制约 CPU 实际处理能力提高的瓶颈。实际应用中,CPU 始终都在等待内存访问。当内存端口满负载时,CPU 核心有超过 50%时间是空闲的。这个问题被称为内存墙(Memory Wall)。中央处理器的速度决定了计算机运算数据及处理信息的快慢,主存储器的容量则决定了计算机可以储存信息的多寡,有些人可能还会去考虑伴随中央处理器的高速缓存(cache memory)的大小,这是因为高速缓存是用来储存一些常常使用到的信息,把这些常常用到的信息放在速度较快的高速缓存中可以使 CPU 很快的取得这些信息,而不需要再到速较慢的主存储器中去寻找,如此一来可使 CPU 处理的速度加快。图 1.1 展示了当前流行的多核处理器的多级缓存架构,每个处理核心有一级指令缓存(L1I Cache)和一级数据缓存(L1D),多个处理核心共享二级缓存(L2 Cache),所有的处理核心共享三级缓存(L3 Cache)。图 1.1 多核处理器架构的多级缓存架构基本上...