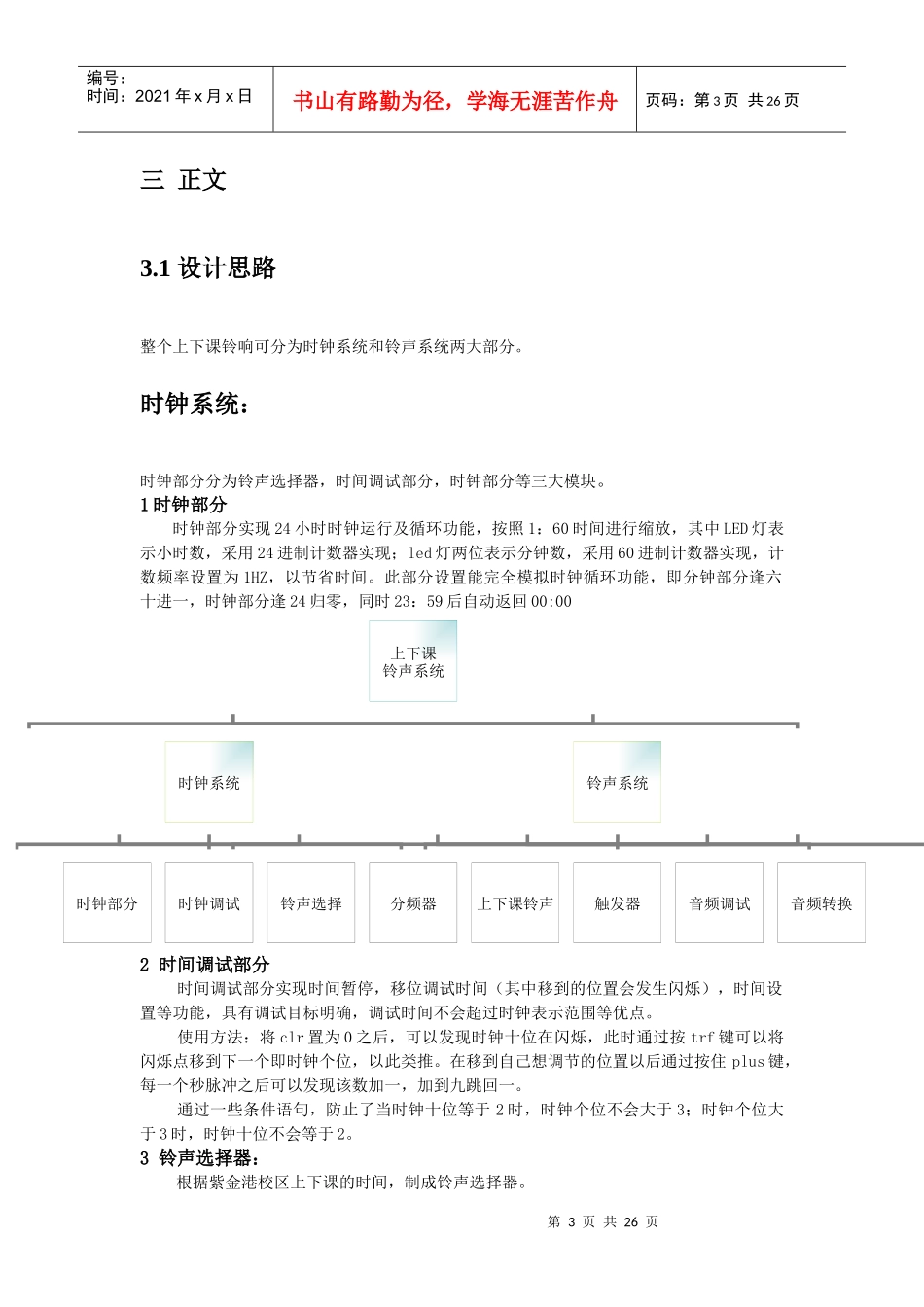

第1页共26页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第1页共26页数字电子技术实验课程FPGA创新实验设计报告设计名称上下课铃声模拟系统姓名林嘉颖金延鑫学号30901007683090104182专业班级机械电子工程0902指导教师樊伟敏日期2011.6.6第2页共26页第1页共26页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第2页共26页浙江大学电工电子基础实验中心一摘要通过QUATURS软件的程序编译及FPGA的应用,模拟出浙江大学紫金港校区的上下课铃系统。该系统分为两部分:电子钟部分和铃声部分电子钟部分将实现二十四小时计时,时间设置等功能。铃声部分将实现特定时间(如上课时间)响起特定铃声功能。二关键词时序电路时钟系统调节装置声音系统QUATURS应用第3页共26页第2页共26页上下课铃声系统时钟系统铃声系统时钟部分铃声选择时钟调试分频器音频转换音频调试触发器上下课铃声编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第3页共26页三正文3.1设计思路整个上下课铃响可分为时钟系统和铃声系统两大部分。时钟系统:时钟部分分为铃声选择器,时间调试部分,时钟部分等三大模块。1时钟部分时钟部分实现24小时时钟运行及循环功能,按照1:60时间进行缩放,其中LED灯表示小时数,采用24进制计数器实现;led灯两位表示分钟数,采用60进制计数器实现,计数频率设置为1HZ,以节省时间。此部分设置能完全模拟时钟循环功能,即分钟部分逢六十进一,时钟部分逢24归零,同时23:59后自动返回00:002时间调试部分时间调试部分实现时间暂停,移位调试时间(其中移到的位置会发生闪烁),时间设置等功能,具有调试目标明确,调试时间不会超过时钟表示范围等优点。使用方法:将clr置为0之后,可以发现时钟十位在闪烁,此时通过按trf键可以将闪烁点移到下一个即时钟个位,以此类推。在移到自己想调节的位置以后通过按住plus键,每一个秒脉冲之后可以发现该数加一,加到九跳回一。通过一些条件语句,防止了当时钟十位等于2时,时钟个位不会大于3;时钟个位大于3时,时钟十位不会等于2。3铃声选择器:根据紫金港校区上下课的时间,制成铃声选择器。第4页共26页第3页共26页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第4页共26页以下为响铃时间安排表:上课铃下课铃8:008:458:509:359:5010:3510:4011:2511:3012:1513:1514:0014:0514:5014:5515:4015:5516:4016:4517:3018:3019:1519:2020:0520:1020:55根据时间表在相应时间,铃声响起。铃声部分铃声部分分为JK触发器,分频器,铃声部分,选择器,音频调试,音频转换器,六个模块。1分频器分频器将50MHZ的脉冲电路调节到合适的频率,在铃声系统部分中需使用两次,一次为对上下课铃音频电路的触发(1HZ),一次为音频转换器的触发(6250000HZ).2铃声部分铃声部分设置成上课铃和下课铃两个子模块,分别存放上下课铃的乐谱。3音频调试电路根据十二平均律将两个八度共十六个音符设置成相应的频率。使其转换成相应的音高。4音频转换器原理为一个计数器,通过脉冲电路将每次的音符转换成相应的频率,通过小喇叭输出。5JK触发器整个音乐系统的开始与停止通过两个JK触发器来控制。原理如图当选择器发出信号时,第一个JK触发器中J通道接高,K通道为0,Q输出高电平,使第二个JK触发器触发(第二个JK触发器设置成T’触发器)此后即使第一个触发器中J=0.Q1状态保持,仍为1.在铃声部分设置逻辑出口K,当输出最后一个音符时,k=1,反馈到第一个JK触发器的K端上,此时Q1=0,使第二个触发器清零,停止向铃声部分输送脉冲信号。铃声停止。第5页共26页第4页共26页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第5页共26页3.2实验原理图展示时钟部分VCCBUTTON[0]INPUTPIN_H6VCCSW[2]INPUTVCCBUTTON[1]INPUTPIN_F13PIN_F12PIN_G12PIN_H13PIN_H12PIN_F11PIN_E11HEX0_D[6..0]OUTPUTPIN_A15PIN_E14PIN_B14PIN_A14PIN_C13PIN_B13PIN_A13HEX1_D[6..0]OUTPUTPIN_F14PIN_B17PIN_A17PIN_E15PIN_B16PIN_A16PIN_D15HEX2_D[6..0]OUTPUTPIN_G15PIN_D19PIN_C19PIN_B19PIN_A19PIN_F15PIN_B18HEX3_D[6..0]OU...