数字电子技术综合实验---------MAX+PLUSII快速入门MAX+PLUSII是Altera公司的全集成化可编程逻辑设计环境

它的界面友好,在线帮助完备,初学者也可以很快学习掌握

完成高性能的设计

另外,在进行原理图输入时,可以直接放置74系列逻辑芯片,所以对于普通爱好者来说,即使不使用Altera的可编程器件,也可以把MAX+PLUSII作为逻辑仿真工具,不用搭建硬件电路,即可对自己的设计进行调试,验证

下面以具体实例介绍MAX+PLUSIIV10

功能MAX+PLUSII的编译核心支持Altera的FLEX10K、FLEX8K、MAX9000、MAX7000、FLASHlogic、MAX5000、Classic系列可编程逻辑器件;MAX+PLUSII的设计输入、处理与校验功能一起提供了全集成化的一套可编程逻辑开发工具,可加快动态调试,缩短开发周期;MAX+PLUSII支持各种HDL设计输入,包括VHDL、Verilog和Altera的AHDL;MAX+PLUSII可与其他工业标准设计输入、综合与校验工具链接

与CAE工具的接口符合EDIF200和209、参数化模块库(LPM)、Verilog、VHDL及其它标准

设计者可使用Altera或标准CAE设计输入工具去建立逻辑设计,使用MAX+PLUSII编译器对Altera器件设计进行编译,并使用Altera或其它CAE校验工具进行器件或板级仿真

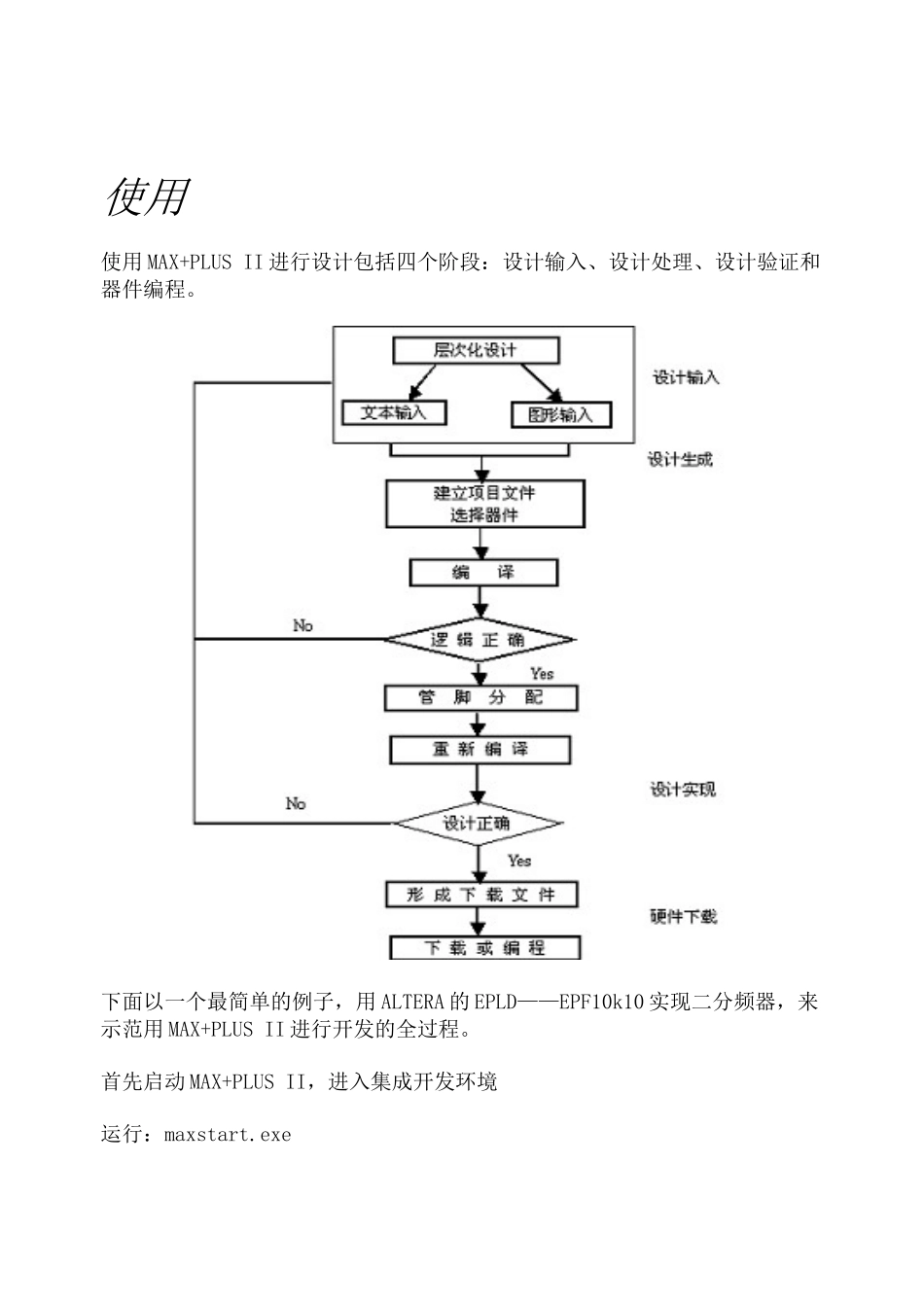

MAX+PLUSII支持与Synopsys、Viewlogic、MentorGraphics、Cadence、Exemplar、DataI/O、Intergraph、Minc、OrCAD等公司提供的工具接口;使用使用MAX+PLUSII进行设计包括四个阶段:设计输入、设计处理、设计验证和器件编程

下面以一个最简单的例子,用ALTERA的EPLD——EPF1