通信与信息工程学院2012/2013学年第二学期软件设计实验报告模块名称二对四译码器专业电子信息工程学生班级B100109学生学号学生姓名指导教师梅中辉、王奇、周晓燕、孔凡坤实验目的:本软件设计的目的和任务:1

使学生全面了解如何应用该硬件描述语言进行高速集成电路设计;2

通过软件使用、设计与仿真环节使学生熟悉EDA-VHDL开发环境;3

通过对基本题、综合题的设计实践,使学生掌握硬件系统设计方法(自底向上或自顶向下),熟悉VHDL语言三种设计风格,并且培养学生应用VHDL语言解决实际问题的能力

实验设备:1:微型计算机2:quartusII开发软件实验课题:2对4译码器实验描述:设计一个2对4译码器(输入:AB输出:Y3Y2Y1Y0),真值表如图:一:实验目的1:能了解组合逻辑中译码器电路的设计原理

2:能利用CPLD数字发展实验系统设计一个二对四译码器

3:能自行验证所设计电路的正确性

二:实验内容及要求设计一个2-4译码器,并验证输出数值的正确性

三:实验器材1

软件:Altera公司的Quartus||软件

ABY3Y2Y1Y00001101111101101101101112

芯片:Altera公司的EP2C8T144C8

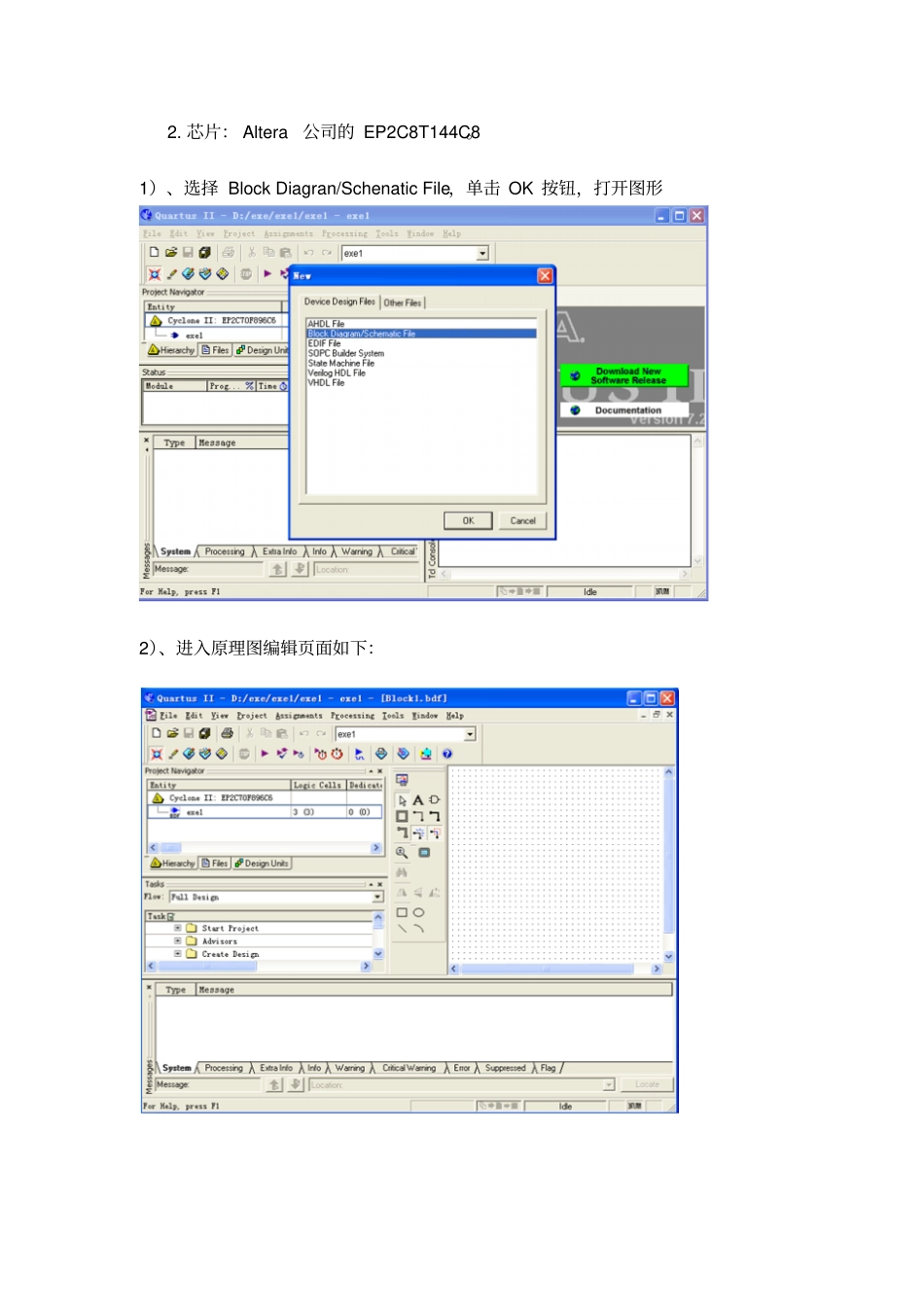

1)、选择BlockDiagran/SchenaticFile,单击OK按钮,打开图形2)、进入原理图编辑页面如下:导入逻辑门电路符号、输入/输出符号,用导线连接各逻辑单元如下:工程建立与编译建立工程:在D盘建立test文件夹,进入quartusII7

2主界面,新建编辑代码页面,选择VHDLfile,点击OK代码输完后存盘,文件名必需为test8(文件名必须与实体名一致),目录为,按project菜单下setastop-levelentity命令

按开始分析与综合按钮(startanalysis&synthesis),出现综合成功对话框