数电日历表课程设计电子课程设计专业:电气工程及其自动化题目:电子日历表学生姓名:xxx学号:xxx指导教师:xxx时间:2011年06月20日~2011年06月23日指导教师评语:成绩:一、设计目的运用所学知识设计一个电子日历表的基本电路,培养运用所学知识解决实际问题,将理论运用到实际的能力,激发学习兴趣

1、掌握计数器、门电路等电子元件的使用方法;2、熟悉采用时序电路设计方法实现课题技术指标与要求;3、设计电子日历表主体电路并了解其工作原理

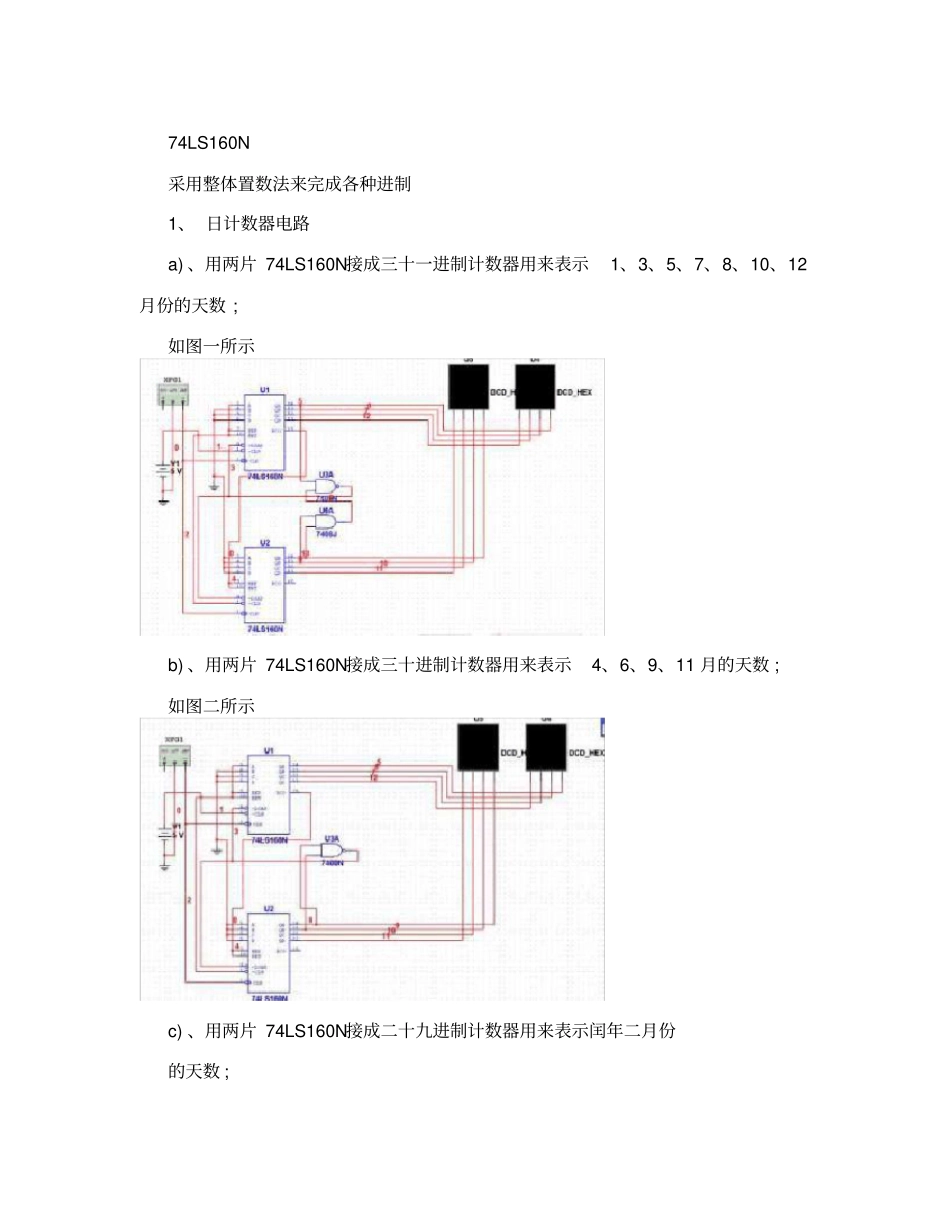

二、设计要求1、电子日历表能够显示五年内的年、月、日;2、使其具有手动校正年、月、日的功能;3、对二月份的天数要求:平年28天,闰年29天

三、设计方案及其比较方案一:对于如此所用元器件比较多的电子设计,电路连接比较复杂,可考虑运用单片机来完成

方案二:采用同步十进制计数器74LS160N的级联来设计年、月、日的电路,设计门电路实现年、月对日的反馈选择,显示部分用普通数码显示管,校正部分采用开关控制高低电平

方案比较:由于所学知识有限,加之电子元器件价格便宜,因此选择方案二进行设计,经济、可靠,符合当前设计水平

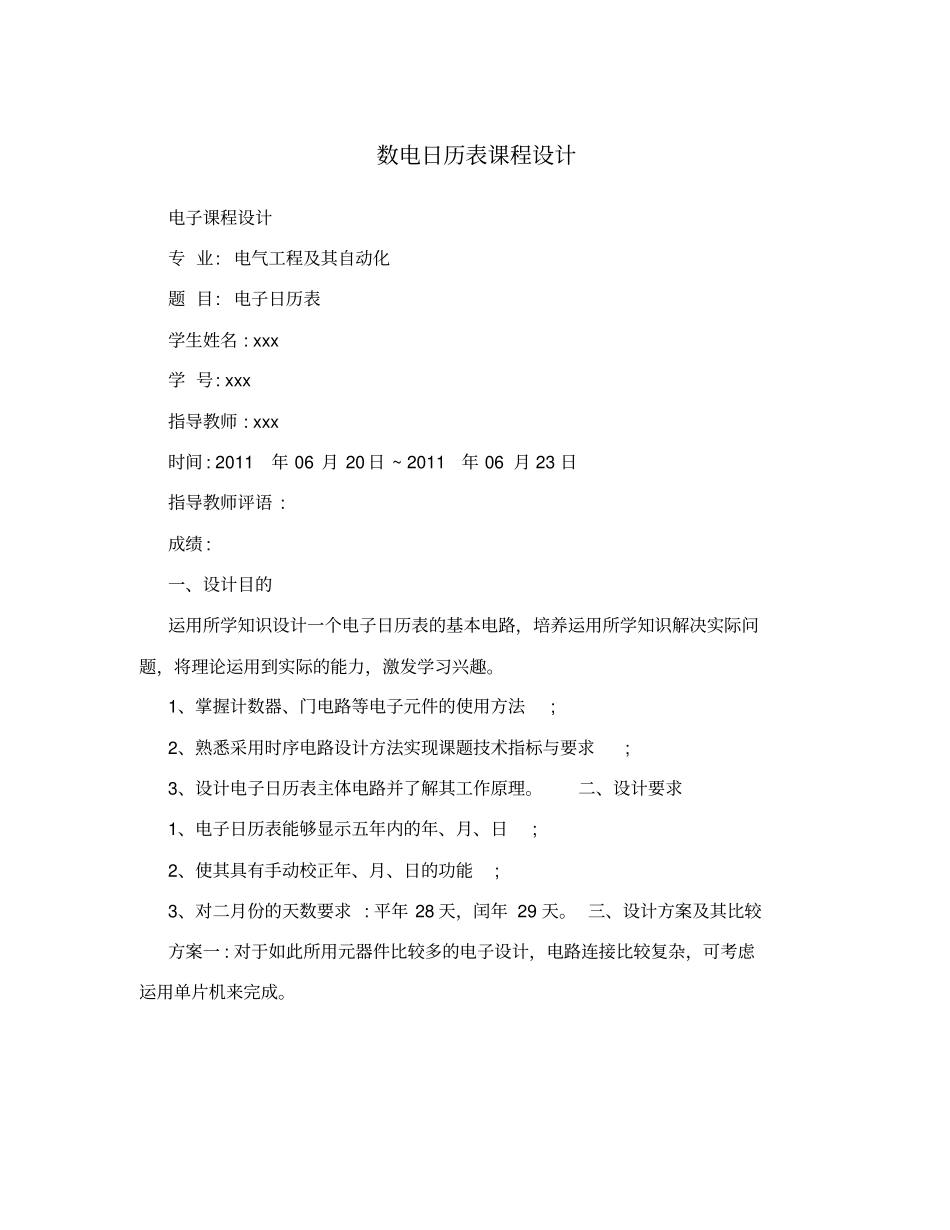

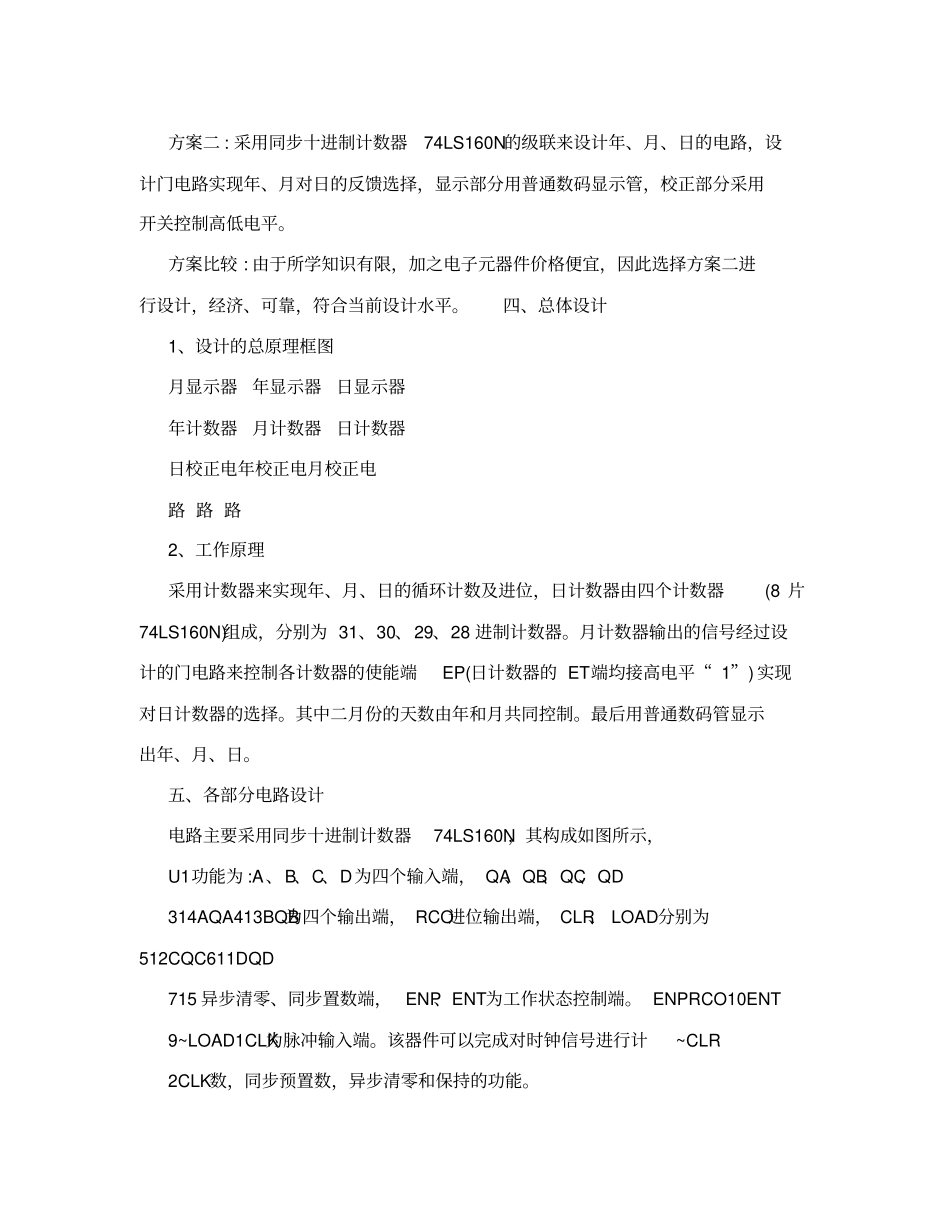

四、总体设计1、设计的总原理框图月显示器年显示器日显示器年计数器月计数器日计数器日校正电年校正电月校正电路路路2、工作原理采用计数器来实现年、月、日的循环计数及进位,日计数器由四个计数器(8片74LS160N)组成,分别为31、30、29、28进制计数器

月计数器输出的信号经过设计的门电路来控制各计数器的使能端EP(日计数器的ET端均接高电平“1”)实现对日计数器的选择

其中二月份的天数由年和月共同控制

最后用普通数码管显示出年、月、日

五、各部分电路设计电路主要采用同步十进制计数器74LS160N,其构成如图所示,U1功能为:A、B、C、D为四个输入端,QA、QB、QC、QD314AQA413BQB为四个输出端,RCO进位输