计算机组成原理第一章计算机系统概论(清楚一个概念)计算机的性能指标:吞吐量:表征一台计算机在某个时间间隔内能够处理的信息量

响应时间:表征从输入有效到系统产生响应之间的时间度量,用时间单位来度量

利用率:在给定的时间间隔内系统被实际使用的时间所占的比率,用百分比表示

处理机字长:指处理机运算器中一次能够完成二进制数运算的位数

总线宽度:一般指CPU中运算器与存储器之间进行互连的内部总线二进制位数

存储器容量:存储器中所有存储单元的总数目,通常KB,MB,GB,TB来表示

存储器带宽:单位时间内存储器读出的二进制数信息量,一般用字节数/秒表示

主频/时钟周期:CPU的工作节拍受主时钟控制,主时钟不断产生固定频率的时钟,主时钟的频率叫CPU的主频

度量单位MHZ(兆赫兹)、GHZ(吉赫兹)主频的倒数称为CPU时钟周期(T),T=1/f,度量单位us,nsCPU执行时间:表示CPU执行一般程序所占的CPU时间,公式:CPU执行时间=CPU时钟周期数xCPU时钟周期CPI:表示每条指令周期数,即执行一条指令所需的平均时钟周期数

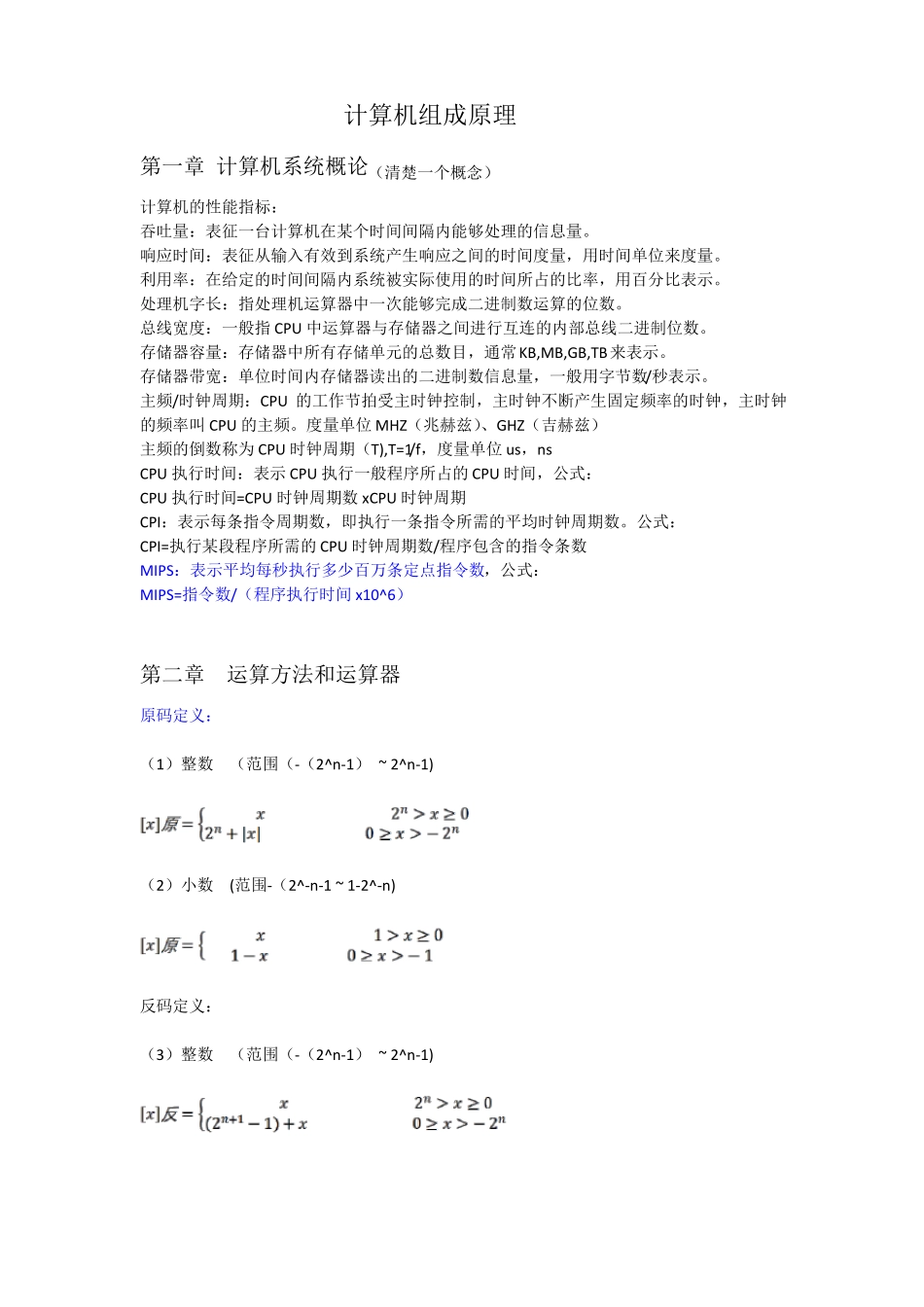

公式:CPI=执行某段程序所需的CPU时钟周期数/程序包含的指令条数MIPS:表示平均每秒执行多少百万条定点指令数,公式:MIPS=指令数/(程序执行时间x10^6)第二章运算方法和运算器原码定义:(1)整数(范围(-(2^n-1)~2^n-1)(2)小数(范围-(2^-n-1~1-2^-n)反码定义:(3)整数(范围(-(2^n-1)~2^n-1)(4)小数(范围-(2^-n-1~1-2^-n)补码定义:(5)整数(范围(-(2^n)~2^n-1)(6)小数(范围(-1~1-2^-n)移码表示法(用于大小比较与对阶操作)IEEE754标准格式:符号位(1位)+阶码(移码)+尾数正溢:两个正数相加,结果大于机器字长所能表示的最大正数负溢:两个负数相加,结果小